ARMY TM 11-5895-389-34-1 NAVY NAVELEX 0967-LP-377-7020 AIR FORCE TO 31R5-2TSC54-22-1

#### DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL

## SATELLITE COMMUNICATION TERMINAL AN/TSC-54 (FUNCTIONAL ANALYSIS) (NSN 5895-00-937-4993)

This copy is a reprint which includes current pages from Changes 1 through 3.

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE

**JANUARY 1978**

The following are general safety precautions that are not related to any specific procedures and, therefore, do not appear elsewhere in this publication. These are recommended precautions that personnel must understand and apply during many phases of operation and maintenance.

#### **WARNINGS**

Maintenance personnel should be familiar with the safety requirements before attempting maintenance or operation of the equipment covered by this manual. Failure to follow requirements and observe safety precautions could result in injury or DEATH.

HIGH VOLTAGE is used in this equipment. DEATH ON CONTACT may result if safety precautions are not observed. Don't take chances.

#### DANGEROUS VOLTAGES EXIST IN THE FOLLOWING UNITS:

| Electronic Equipment Shelter S-378/TSC-54         | 208 volts ac     |

|---------------------------------------------------|------------------|

| Trailer-Mounted Diesel Engine Generator Set       | 208 volts ac     |

| Antenna-Receiver-Transmitter Group OA-8244/TSC-54 |                  |

|                                                   | -13,000 volts dc |

The shelter must be ventilated at all times when occupied by personnel. Open the exhaust vent and air intake doors and operate the blower fans for ventilation.

Under no circumstances should any personnel reach within or enter an equipment inclosure for the purpose of servicing or adjusting the equipment without the immediate presence or assistance of another person capable of rendering aid.

Exhaust gases produced by diesel engine generator sets are POISONOUS. Inhalation may result in illness or DEATH. Provide adequate ventilation if the generator sets are operated in inclosed or covered areas. Exhaust gas pickup by air conditioners should be carefully avoided.

Do not operate or perform maintenance on the generator sets without a suitable ground connection. Electrical defects in the unit, load lines, or load equipment can cause DEATH by electrocution when contact is made with an ungrounded system.

Maintenance personnel should be familiar with the requirements of TB SIG 291 before attempting maintenance on the antenna.

In troubleshooting, it may be necessary to close interlock switches with a unit inclosure open. Extreme care must be observed under such conditions to avoid physical contact with live circuits. This equipment employs voltages which are dangerous and may prove FATAL if proper safety precautions are not observed.

Performance of any field expedient repair creates a condition possibly dangerous to equipment and personnel. The equipment so repaired, should be taken out of service as soon as possible for replacement of the defective parts.

The C-field and 1 PPS of the cesium beam frequency standard will not be adjusted except by direction from the U.S. Naval Observatory (NAVOBSY). The NAVOBSY will give the new setting of the C-field dial control or the six TIME DELAY thumbwheel switches to be adjusted. The instructions and procedures for the operation and reporting of data is contained in the NAVOBSY TS/TT1-O/M.

Change No. 3

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE Washington, DC, 2 February 1981

### **Direct Support and General Support Maintenance Manual**

#### **SATELLITE COMMUNICATION TERMINAL AN/TSC-54**

(FUNCTIONAL ANALYSIS)

(NSN 5895-00-937-4993)

TM 11-5895-389-34-1 NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1, 5 January 1978, is changed as follows:

- 1. Changed material on illustrations is indicated by a pointing hand.

- 2. Remove old pages and insert new pages as indicated below:

| Remove                  | Insert                  |

|-------------------------|-------------------------|

| Figure FO 2-3 (sheet 4) | Figure FO 2-3 (sheet 4) |

| Figure FO 2-10          | Figure FO 2-10          |

3. File this change sheet in front of the manual for reference purposes.

#### TM 11-5895-389-34-1/NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1

By Order of the Secretaries of the Army, the Navy, and the Air Force:

E. C. MEYER General, United States Army Chief of Staff

Official:

J. C. PENNINGTON

Major General, United States Army

The Adjutant General

H. D. ARNOLD Rear Admiral, United States Navy Commander, Naval Electronic Systems Command

> LEW ALLEN JR., General USAF Chief of Staff

Official:

BRYCE POE, II, General, USAF Commander, Air Force Logistics Command

**DISTRIBUTION:**

To be distributed in accordance with DA Form 12-51, Direct and General Support maintenance requirements for AN/TSC-54.

Change No. 2

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE Washington, DC, 10 June 1980

### **Direct Support and General Support Maintenance Manual**

### **SATELLITE COMMUNICATION TERMINAL AN/TSC-54**

(FUNCTIONAL ANALYSIS)

(NSN 58960-9374993

TM 11-5895-389-34-1/NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1, 5 January 1978, is changed as follows:

- 1. New or changed material is indicated by a vertical bar in the margin.

- 2. Remove old pages and insert new pages as indicated below:

| Remove                  | Insert                     |

|-------------------------|----------------------------|

| 1-3 through 1-6         | 1-3 through 1-7            |

| 2-29 and 2-30           | 2-29 and 2-30              |

| 2-33 and 2-34           | 2-33 and 2-34              |

| 2-49 and 2-50           |                            |

| None                    | Figure FO 2-2 (sheet 14.1) |

| Figure FO 2-9 (sheet 1) | Figure FO 2-9 (sheet 1)    |

3. File this change sheet in front of the manual for reference purposes.

By Order of the Secretaries of the Army, the Navy, and the Air Force:

E. C. MEYER General, United States Army Chief of Staff

Official:

J. C. PENNINGTON Major General, United States Army The Adjutant General

EARL B. FOWLER

Rear Admiral, United States Navy

Commander, Naval Electronic Systems

Command

LEW ALLEN, JR., General USAF Chief of Staff

Official:

BRYCE POE II, General, USAF Commander, Air Force Logistics Command

**DISTRIBUTION:**

To be distributed in accordance with DA Form 12-51, Direct and General Support Maintenance requirements for AN/TSC-54.

CHANGE 1 No. 1

DEPARTMENTS OF THE ARMY, THE NAVY AND THE AIR FORCE WASHINGTON, DC 12 July 1979

### **Direct Support and General Support Maintenance Manual**

#### SATELLITE COMMUNICATION TERMINAL AN/TSC-54 (FUNCTIONAL ANALYSIS)

(NSN 5895-00-937-4993)

TM 11-5895-389-34-1/NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1, 5 January 1978, is changed as follows:

- 1. A vertical bar appears opposite changed material.

- 2. Remove and insert pages as indicated in the page list below:

| Remove                          | Insert                          |

|---------------------------------|---------------------------------|

| i and ii                        | i and ii                        |

| 2-11 through 2-20               | 2-11 through 2-20               |

| 2-23 through 2-26               | 2-23 through 2-26               |

| None                            | Index- 1 and Index 2            |

| None                            | Figure FO 2-1 (sheet 7.1)       |

| Figure FO 2 -1 (sheet 12 of 16) | Figure FO 2-1 (sheet 12 of 16)  |

| Figure FO 2-1 (sheet 14 of 16)  | Figure FO 2-1 (sheet 14 of 16)  |

| Figure FO 2-2 (sheet 10 of 19)  | Figure FO 2 -2 (sheet 10 of 19) |

| Figure FO 2-3 (sheet 1 of 9)    | Figure FO 2-3 (sheet 1 of 9)    |

| Figure FO 2 -3 (sheet 9 of 9)   | Figure FO 2-3 (sheet 9 of 9)    |

| Figure FO 2-4 (sheet 1 of 7)    | Figure FO 2-4 (sheet 1 of 7)    |

| Figure FO 2-4 (sheet 2 of 7)    | Figure FO 2-4 (sheet 2 of 7)    |

| Figure FO 2-4 (sheet 3 of 7)    | Figure FO 2-4 (sheet 3 of 7)    |

| Figure FO 2-4 (sheet 6 of 7)    | Figure FO 2-4 (sheet 6 of 7)    |

| None                            | Figure FO 2-4 (sheet 7.1)       |

| Figure FO 2-7 (sheet 1 of 9)    | Figure FO 2-7 (sheet 1 of 9)    |

| Figure FO 2-7 (sheet 4 of 9)    | Figure FO 2-7 (sheet 4 of 9)    |

| Figure FO 2-7 (sheet 5 of 9)    | Figure FO 2-7 (sheet 5 of 9)    |

| Figure FO 2-7 (sheet 9 of 9)    | Figure FO 2-7 (sheet 9 of 9)    |

| Figure FO 2-8 (sheet 6 of 10)   | Figure FO 2-8 (sheet 6 of 10)   |

| Figure FO 2-9 (sheet 2 of 3)    | Figure FO 2-9 (sheet 2 of 3)    |

| Figure FO 2-10                  | Figure FO 2-10                  |

3. File this change sheet in the front of the manual for reference purposes.

By Order of the Secretaries of the Army, the Navy, and the Air Force:

Official:

J. C. PENNINGTON Major General, United States Army The Adjutant General BERNARD W. ROGERS General, United States Army Chief of Staff

EARL B. FOWLER Rear Admiral, United States Navy Commander, Naval Electronics Systems Command

### TM 11-5895-389-34-1 /NAVELEX O967-LP-377-7020/TO 31R5-2TSC54-22-1

LEW ALLEN, JR., General USAF Chief of Staff

Official:

BRYCE POE II General, USAF, Commander, Air Force Logistics Command

### DISTRIBUTION:

To be distributed in accordance with DA Form 12-51, Direct and General Support maintenance requirements for AN/TSC-54.

TECHNICAL, MANUAL

No. 11-5895-389-34-1

NAVELEX 0967-LP-377-7020

TECHNICAL ORDER

No. 31R5-2TSC54-22-1

DEPARTMENTS OF THE ARMY, THE NAVY, AND THE AIR FORCE

WASHINGTON, DC 5 January 1978

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL SATELLITE COMMUNICATION TERMINAL AN/TSC-54 (FUNCTIONAL ANALYSIS) (NSN 5895-00-937-4993)

#### **REPORTING OF ERRORS**

You can improve this manual by recommending improvements using DA Form 2028-2 located in the back of the manual. Simply tear out the self-addressed form, fill it out as shown on the sample, fold it where shown, and drop it in the mail.

If there are no blank DA Forms 2028-2 in the back of your manual, use the standard DA Form 2028 (Recommended Changes to Publications and Blank Forms) and forward to the Commander, US Army Communications and Electronics Materiel Readiness Command, ATTN: DRSEIME-MQ, Fort Monmouth, NJ 07703.

For Air Force, submit AFTO Form 22 (Technical Order System Publication Improvement Report and Reply) in accordance with paragraph 6-5, Section VI, T.O. 00-5-1. Forward direct to prime ALC/MST.

For Navy, mail comments to the Commander, Naval Electronic Systems Command, Training and Publications Management Office, ELEX 04F3, P.O. Box 80337, San Diego, California 92138.

In either case, a reply will be furnished direct to you.

|                                                                              |                                                                                           | Paragraph       | Page          |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|---------------|

| CHAPTER 1.                                                                   | INTRODUCTION                                                                              |                 | 1-1           |

| Section I.                                                                   | General                                                                                   | 1-1             | 1-1           |

| II.                                                                          | Description and data                                                                      | 1-6             | 1-1           |

| CHAPIER 2.                                                                   | FUNCTIONING OF EQUIPMENT                                                                  |                 | 1-1           |

| Section I.                                                                   | Introduction                                                                              | 2-1             | 2-1           |

| II.                                                                          | Transmitting function                                                                     | 2-4             | 2-2           |

| III.                                                                         | Receiving function                                                                        |                 | 2-29          |

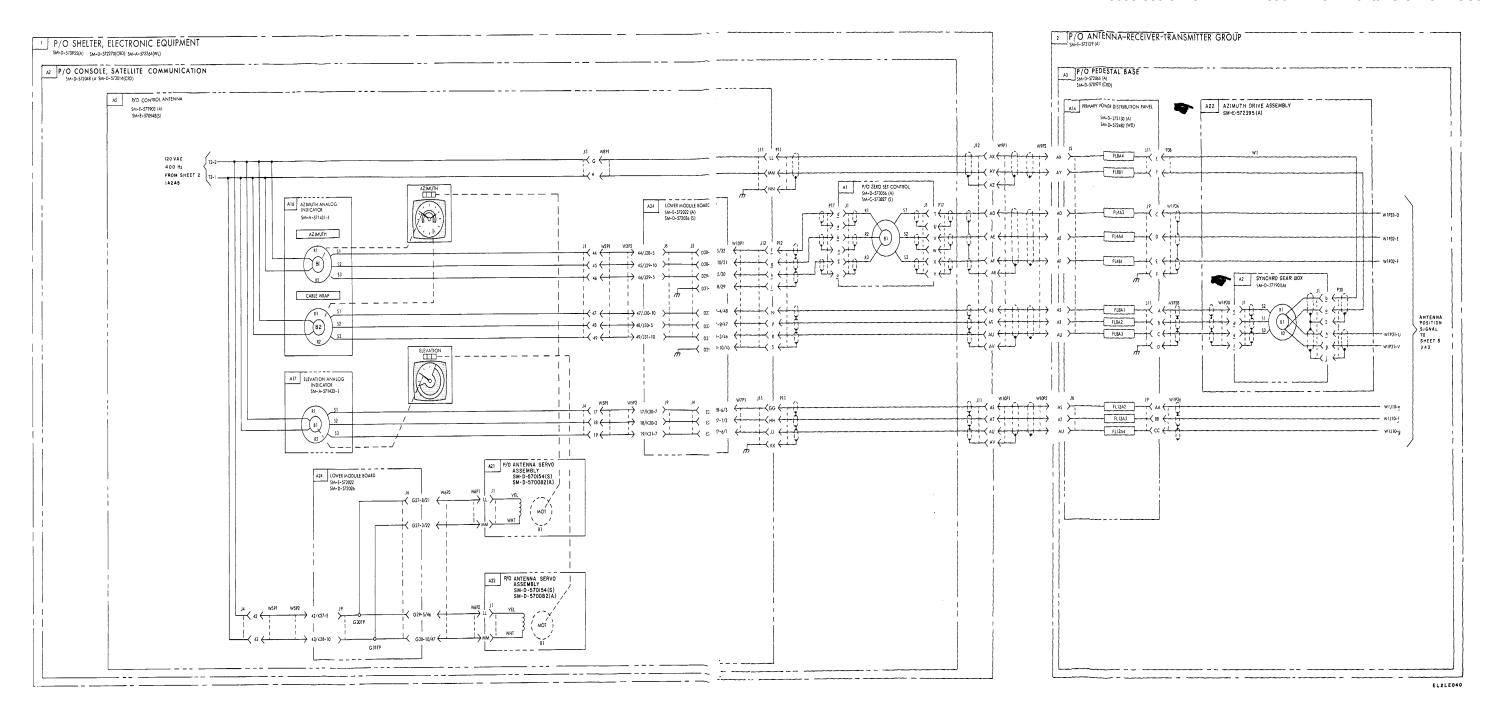

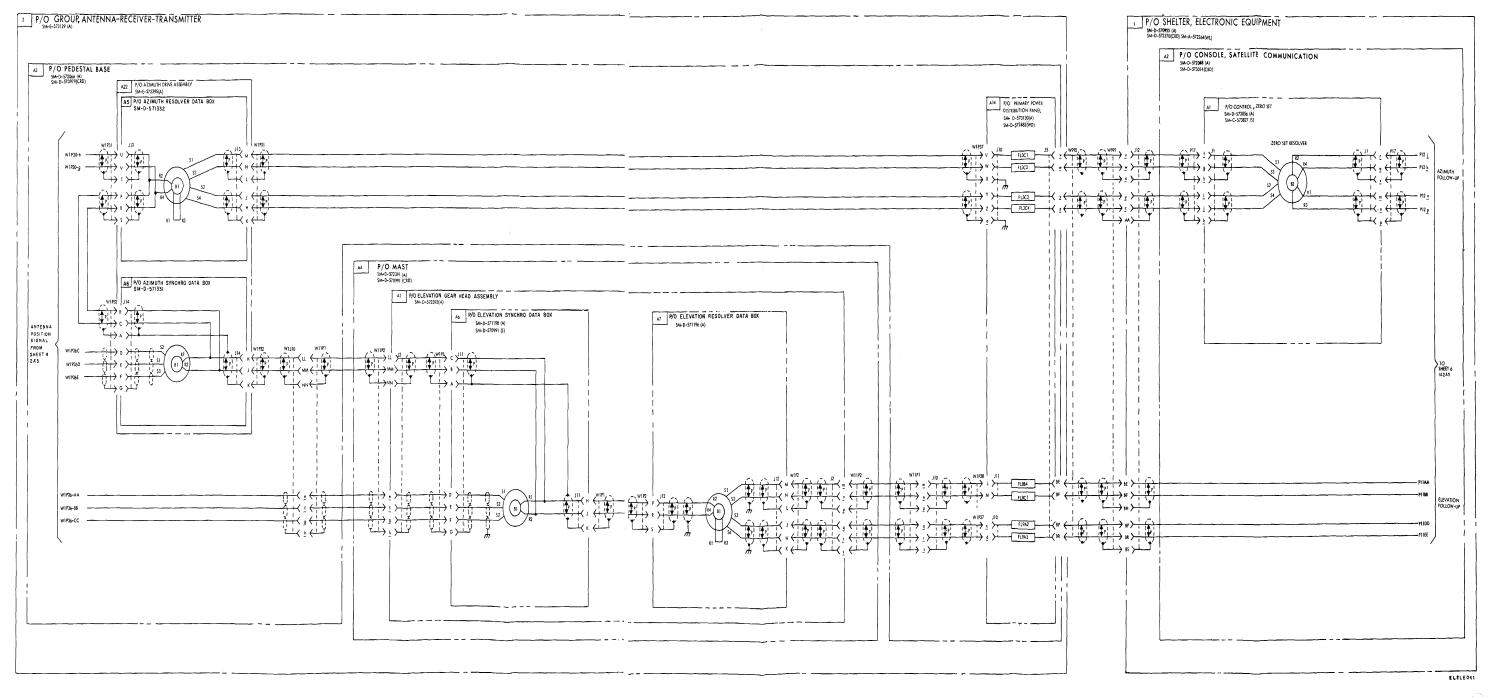

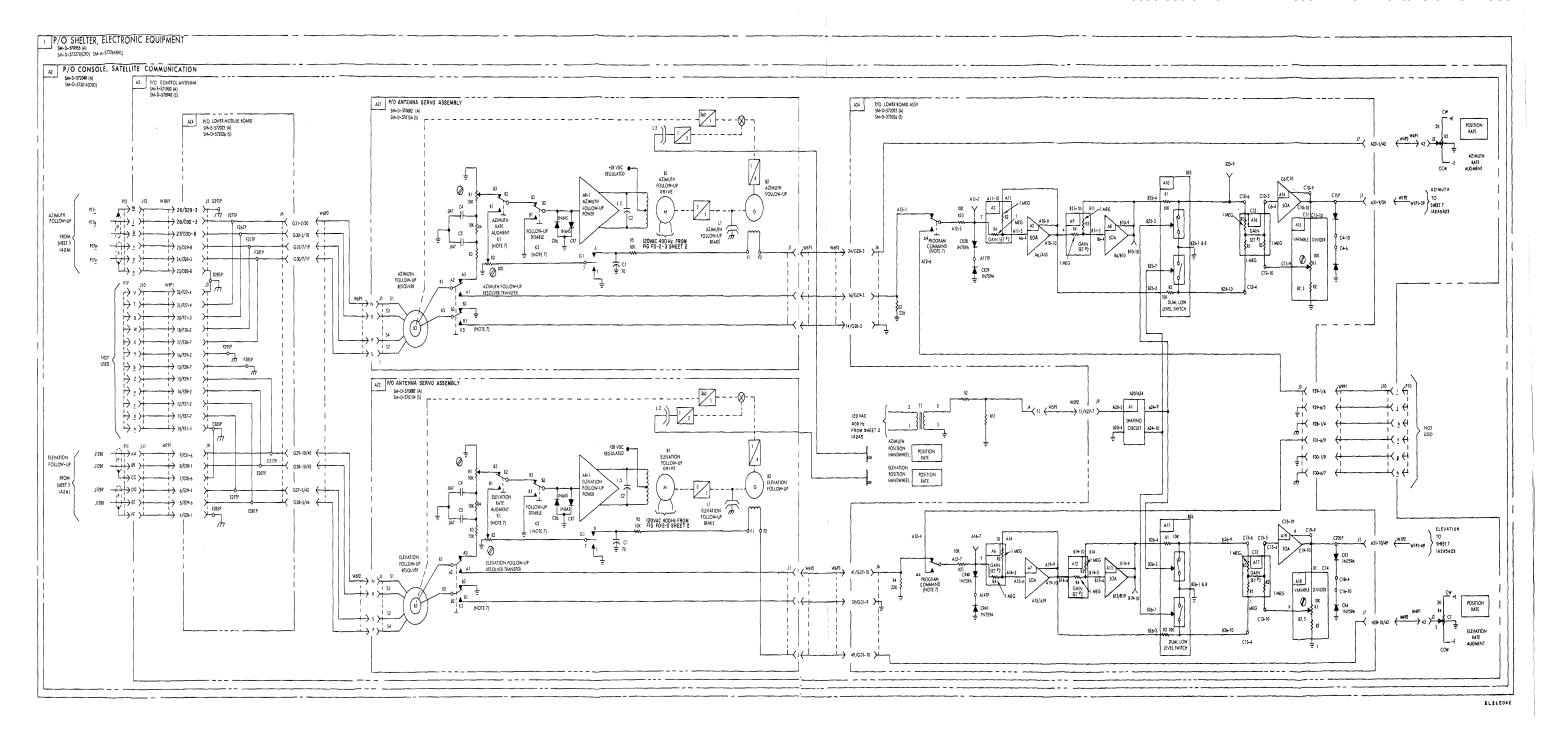

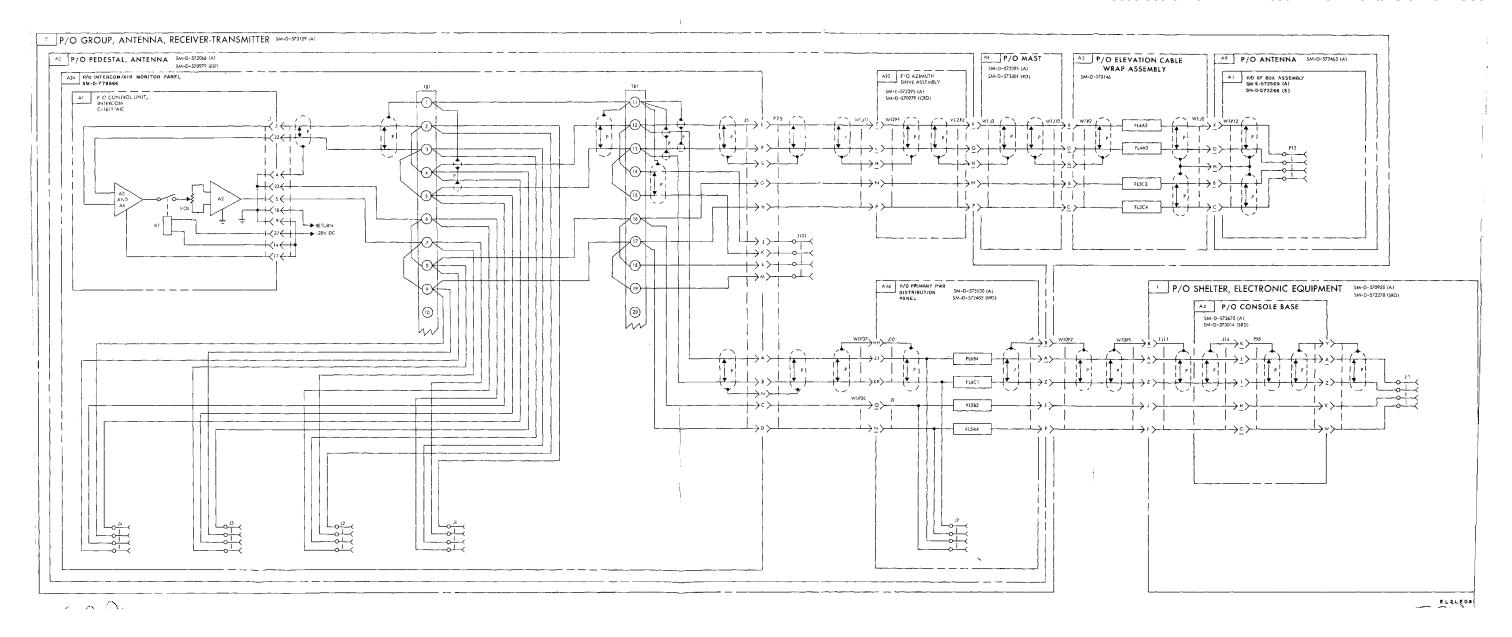

| IV.                                                                          | Antenna control function                                                                  |                 | 2-51          |

| V.                                                                           | Ancillary equipment                                                                       | 2-75            | 2-66          |

| INDEX                                                                        |                                                                                           |                 |               |

|                                                                              | LIST OF ILLUSTRATIONS                                                                     |                 |               |

| Figure                                                                       |                                                                                           |                 |               |

| Number                                                                       | Title                                                                                     |                 | Page          |

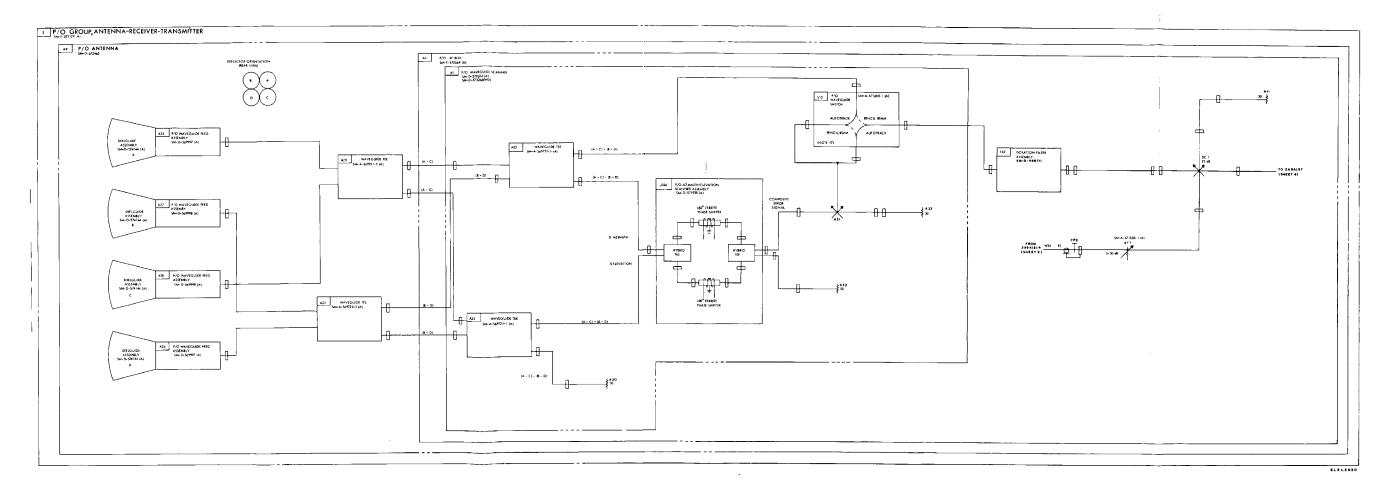

| 1-1                                                                          | Satellite communication terminal AN/TSC-54, simplified block diagram                      |                 | . 1-3         |

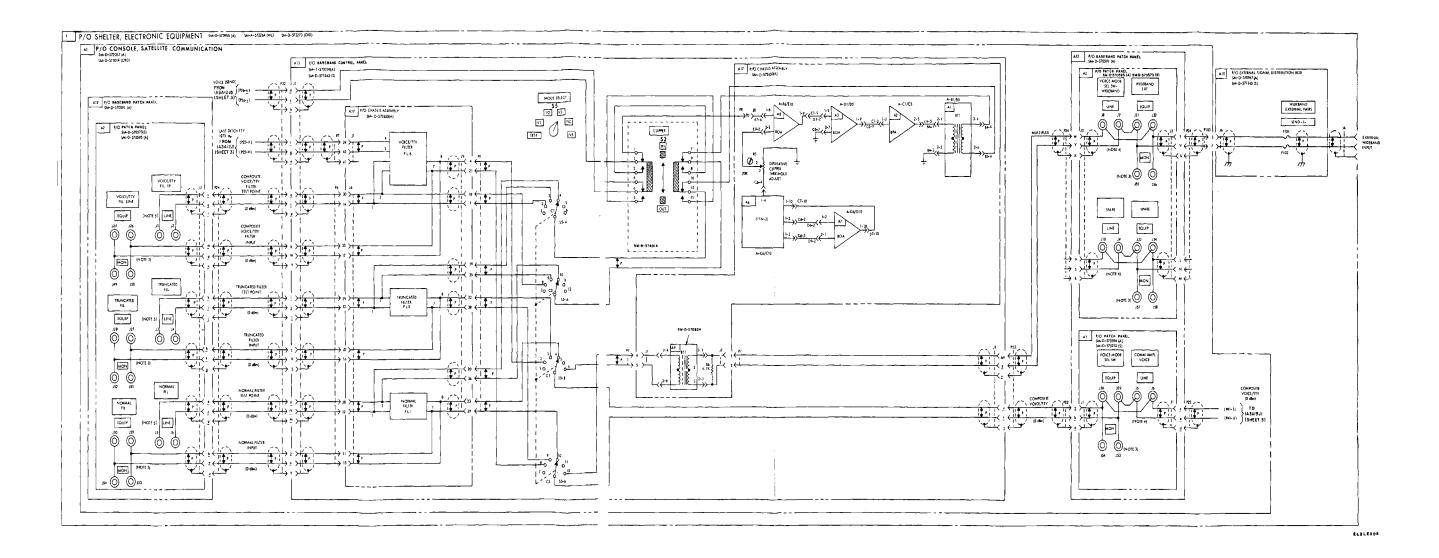

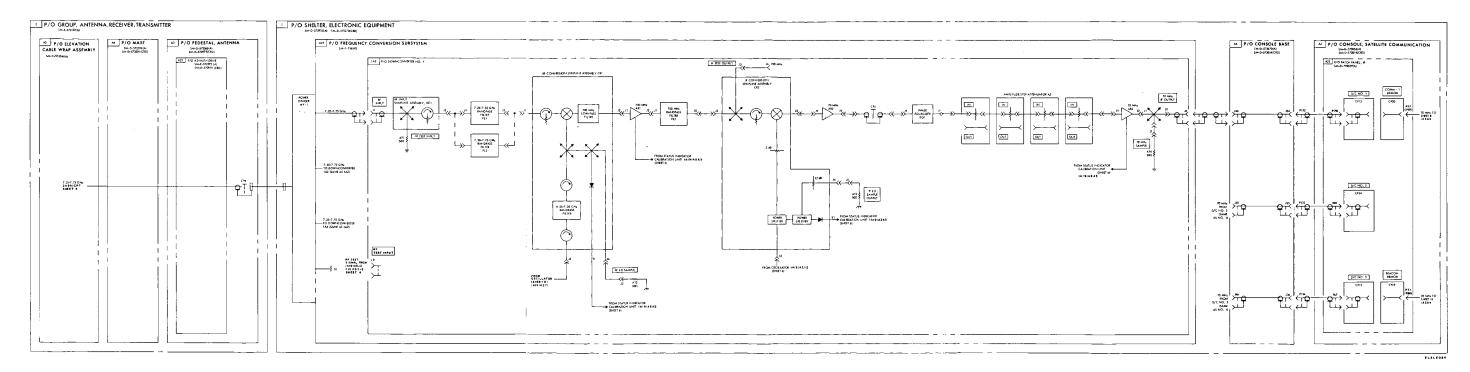

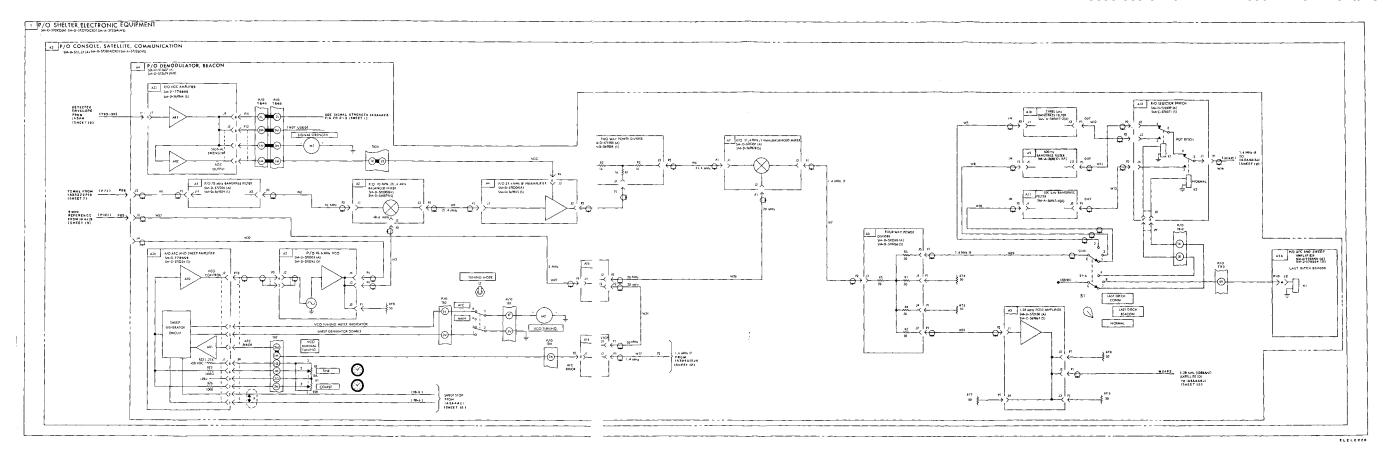

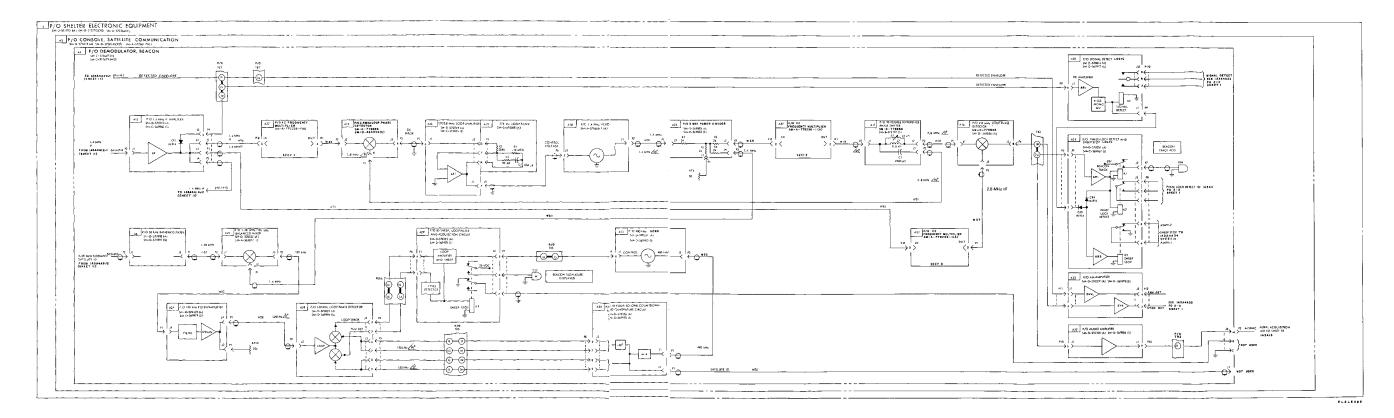

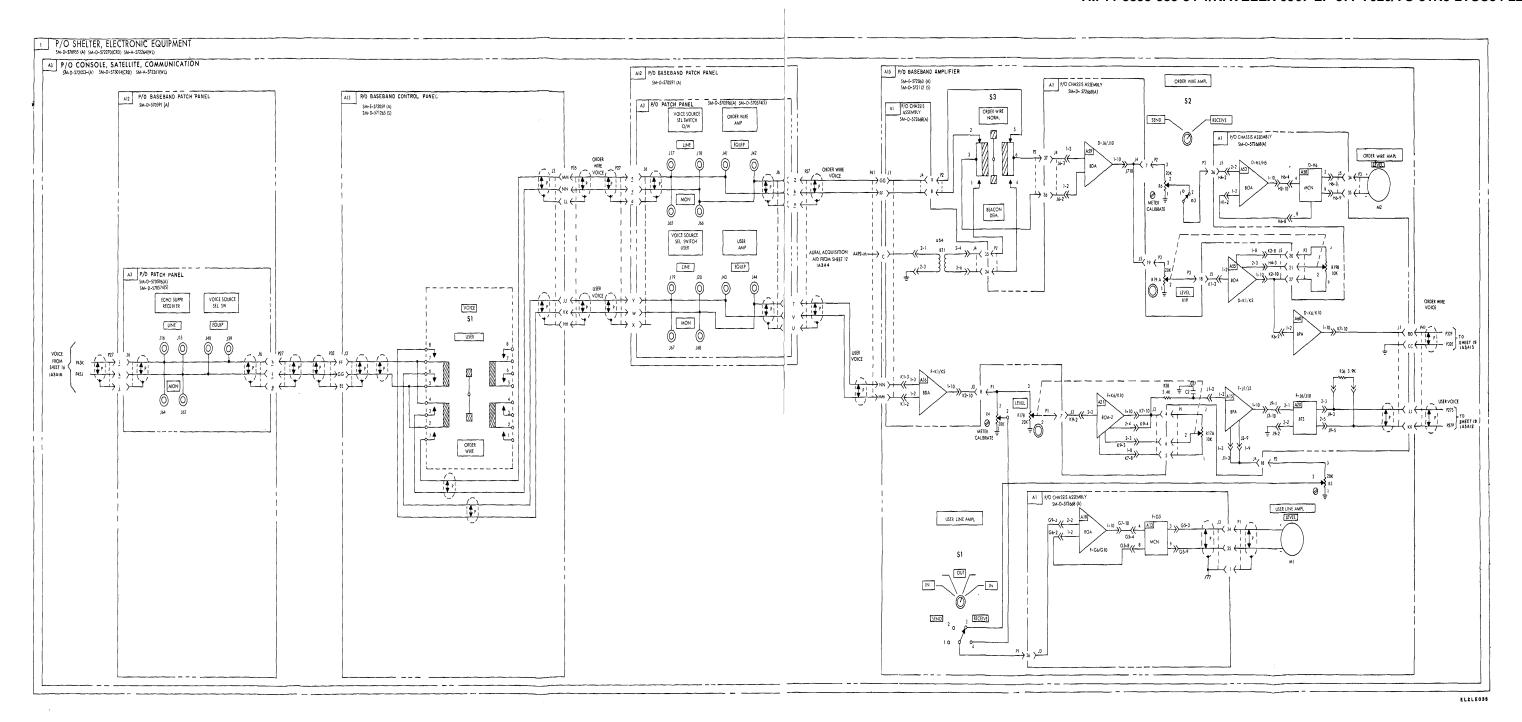

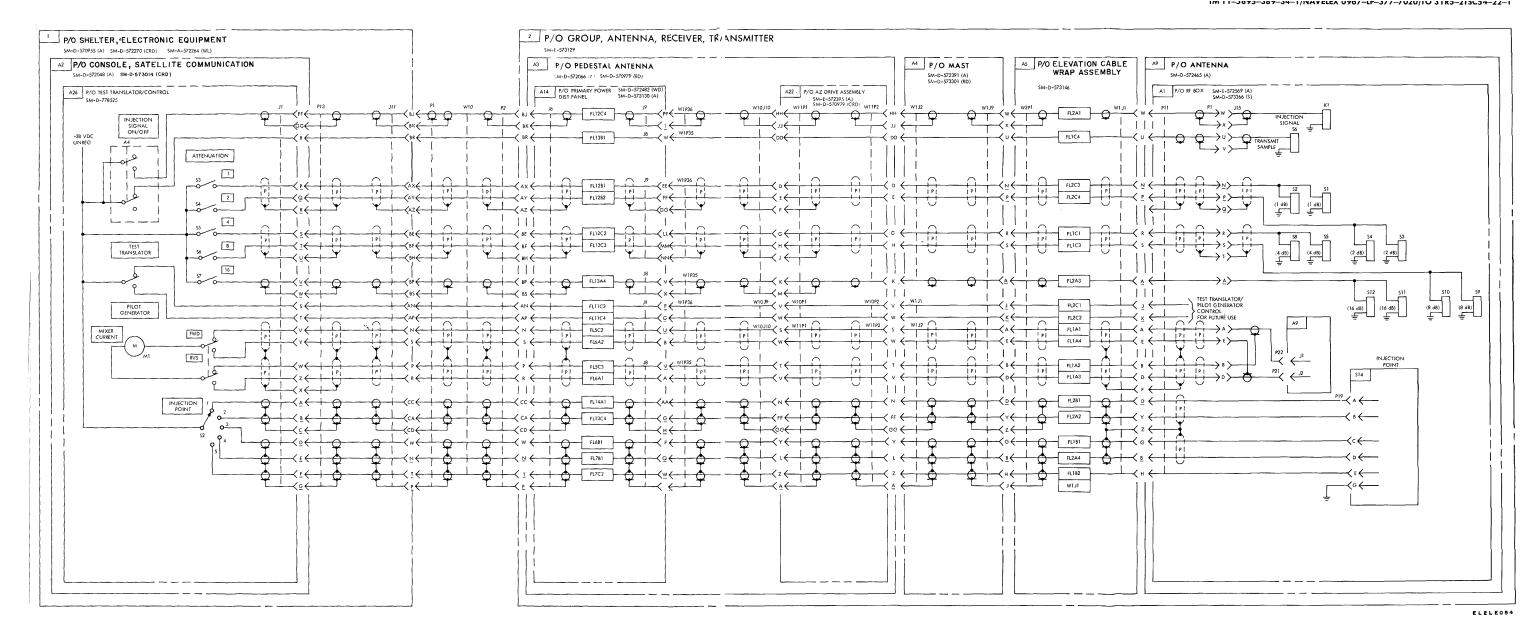

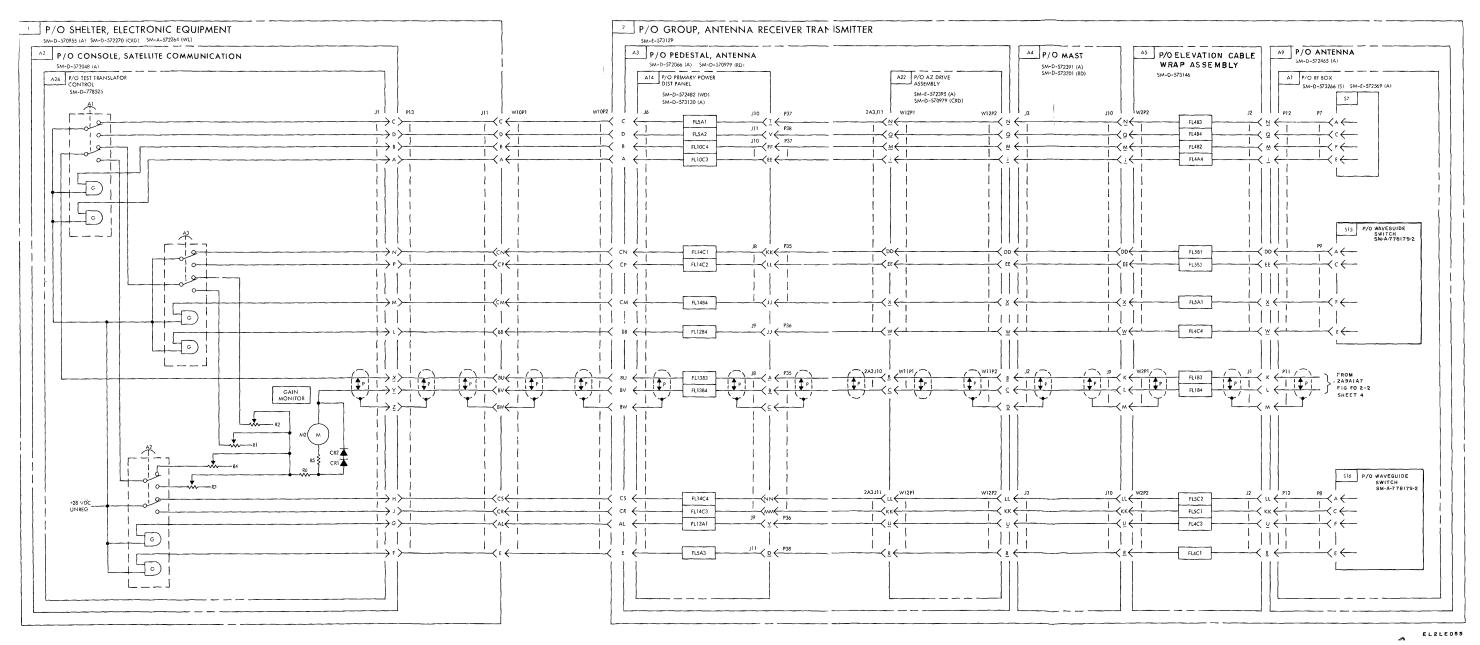

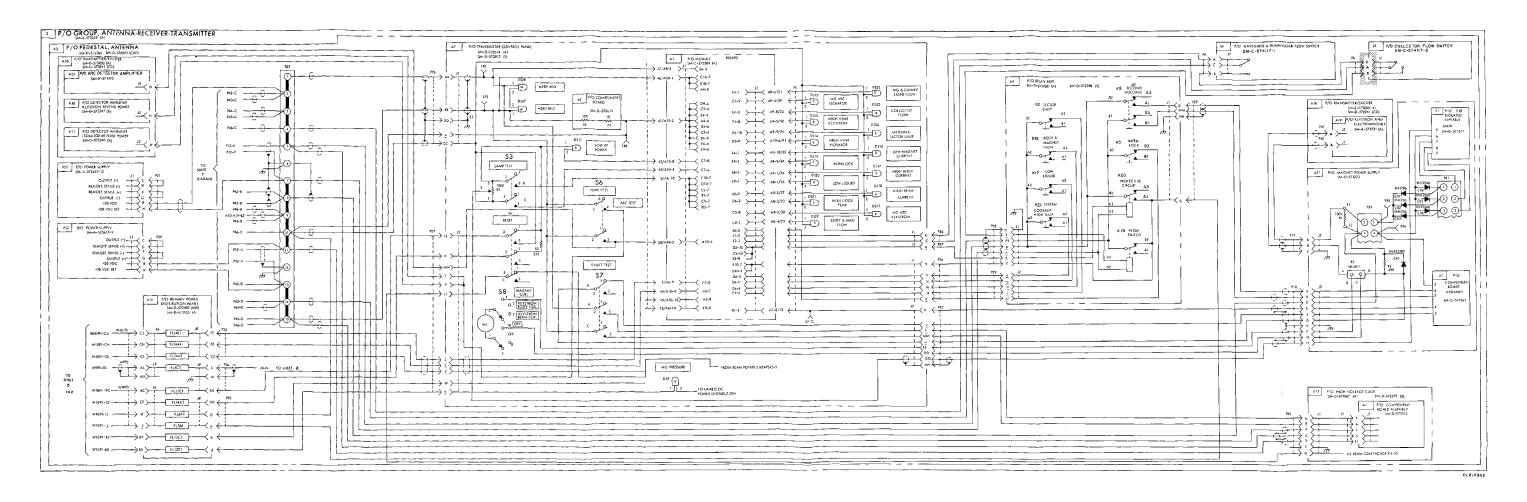

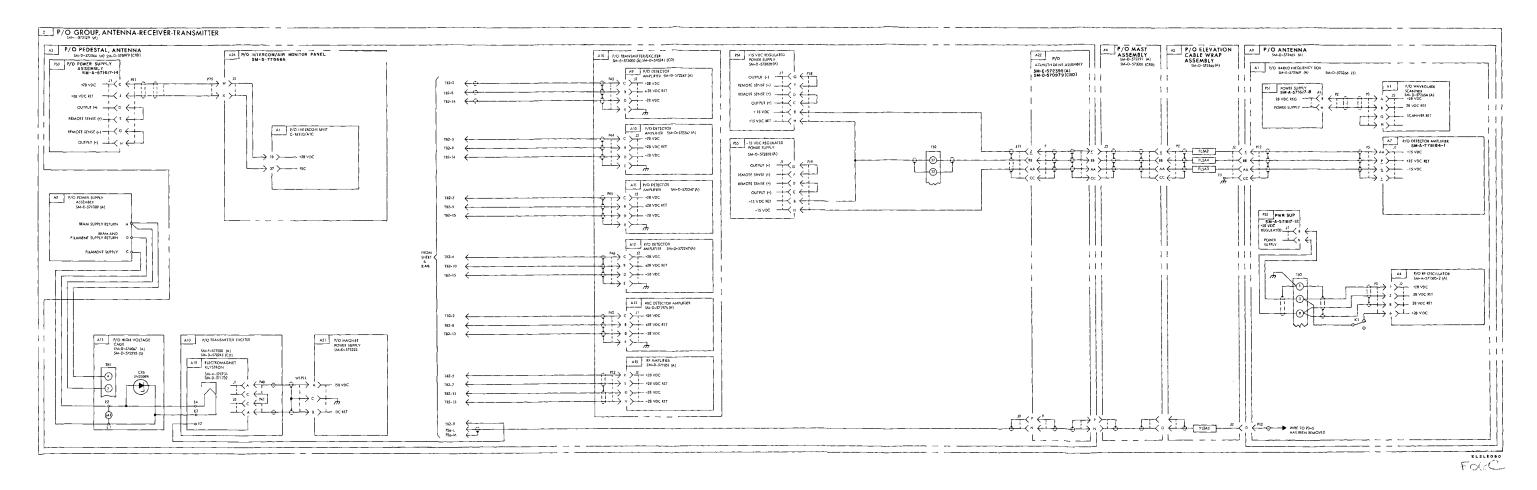

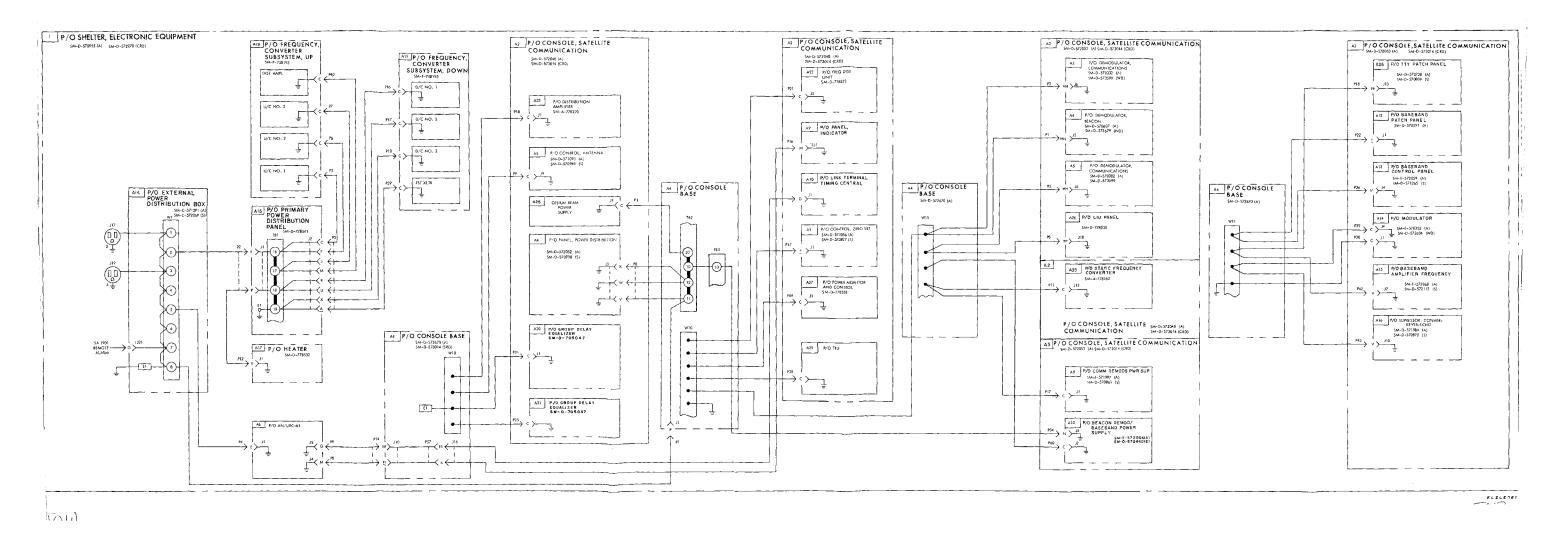

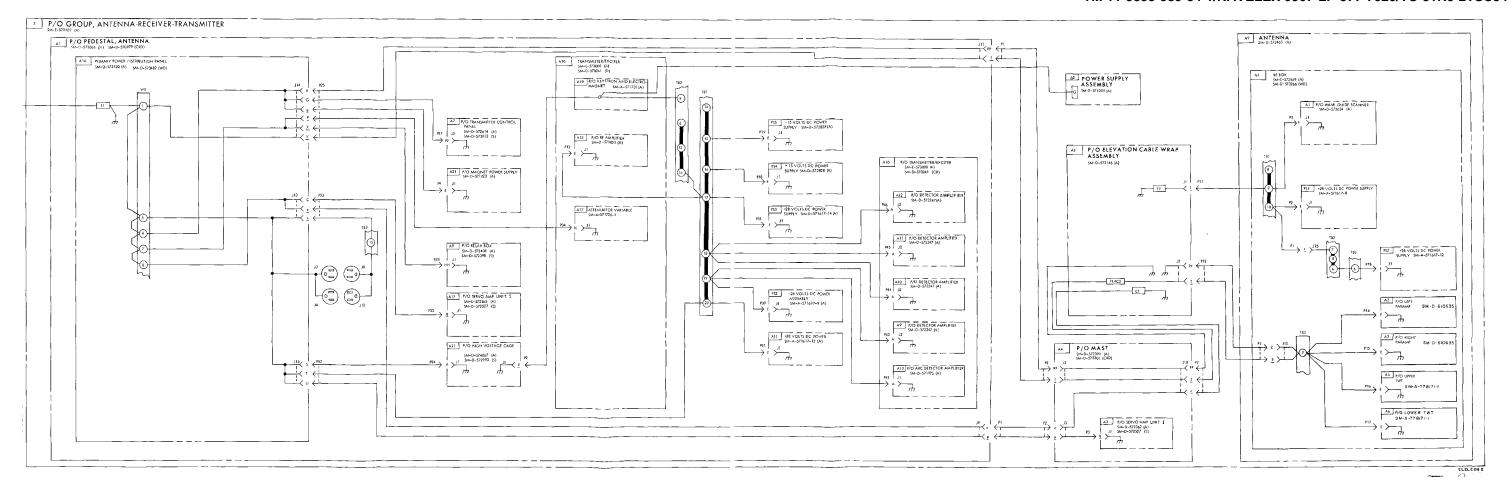

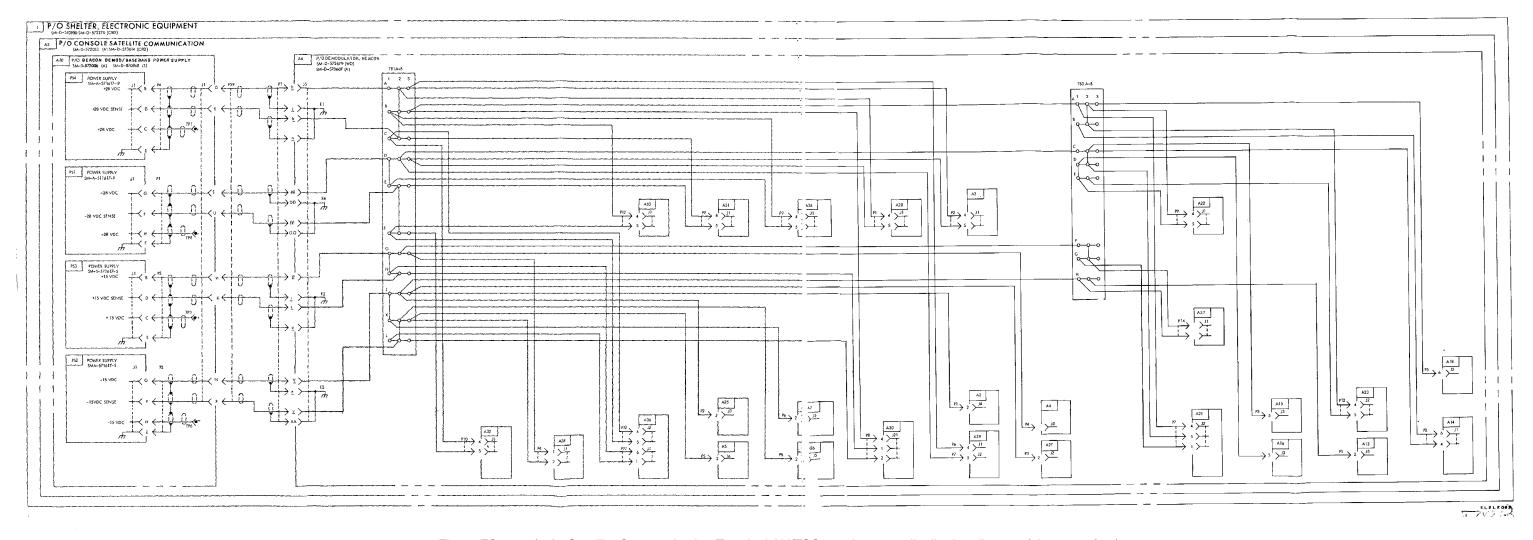

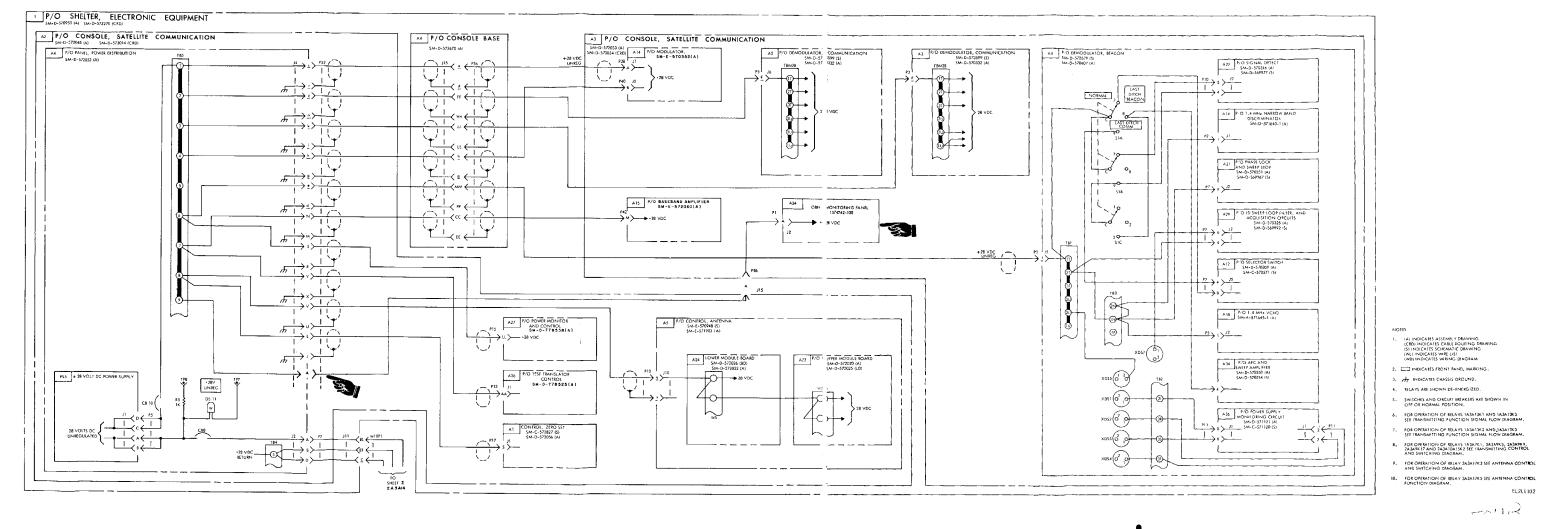

| FO 2-1 <sup>1</sup> through                                                  | Satellite communication terminal AN/TSC- 54, transmitting function, signal flow diagram   | ı (16 sheets) . | illustrations |

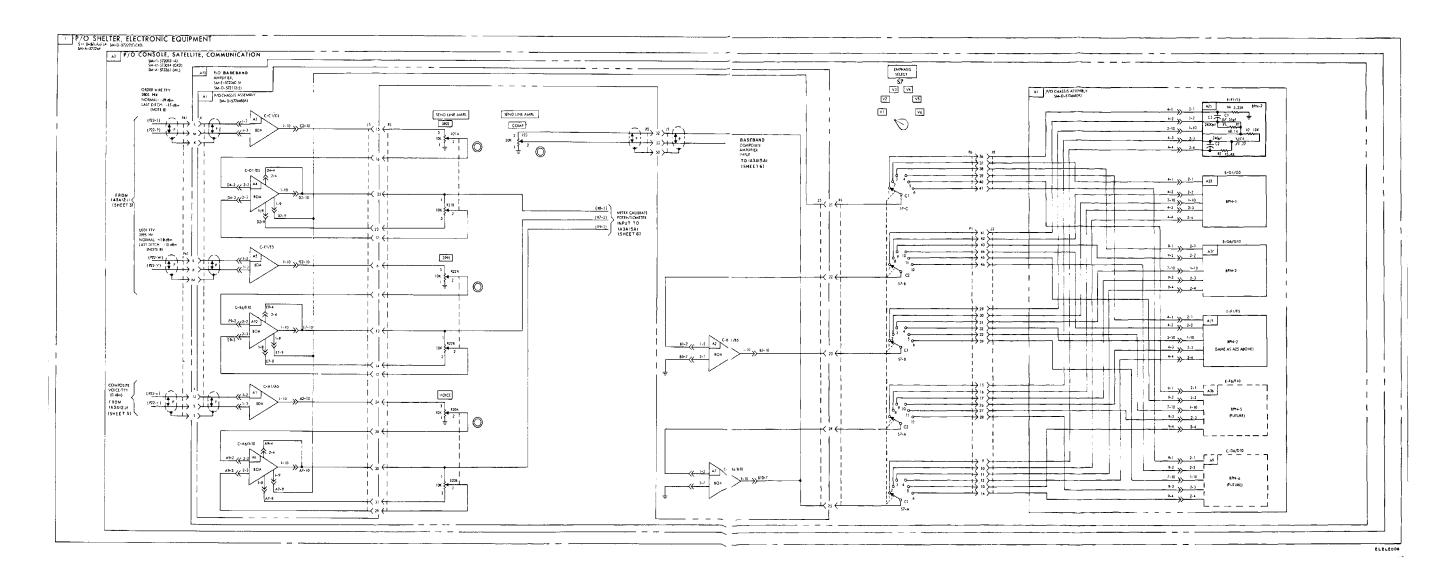

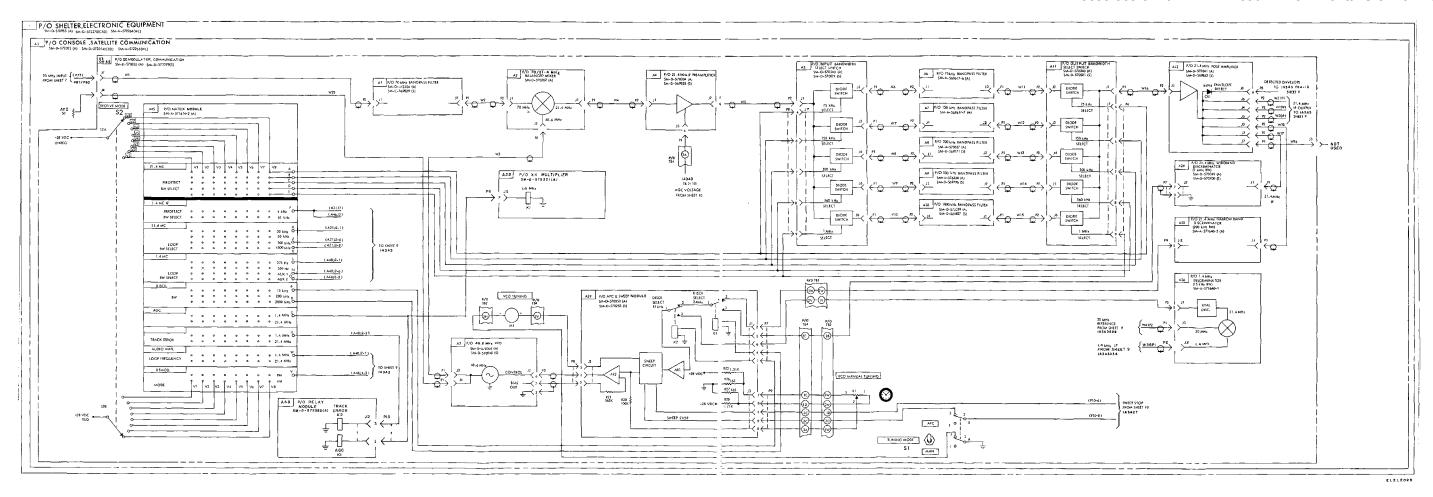

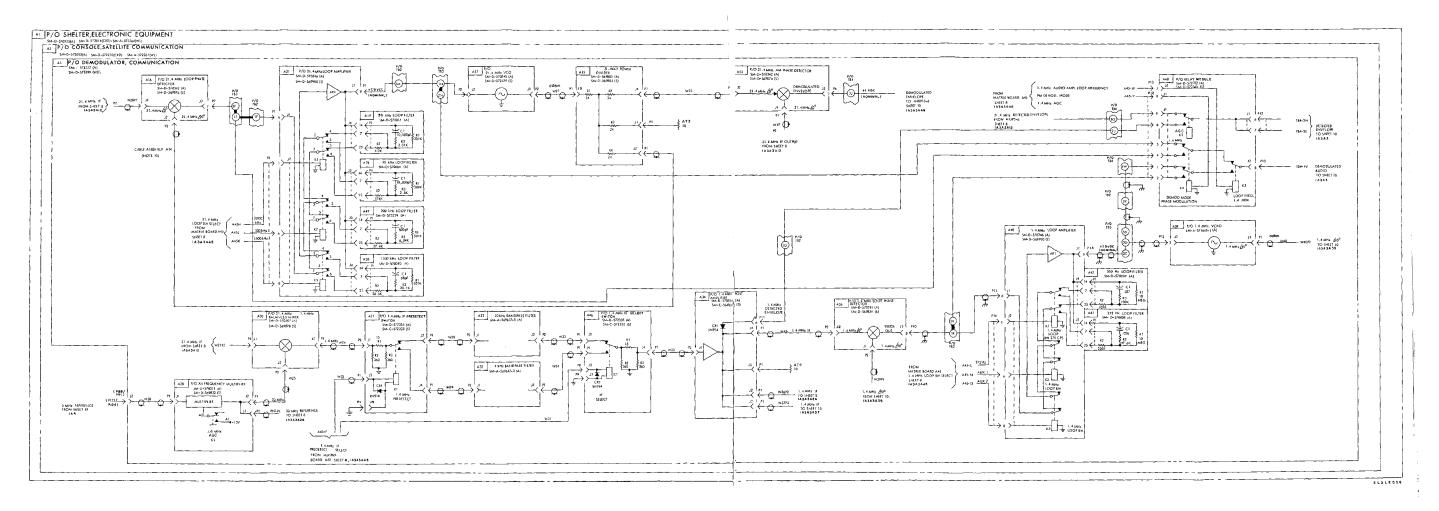

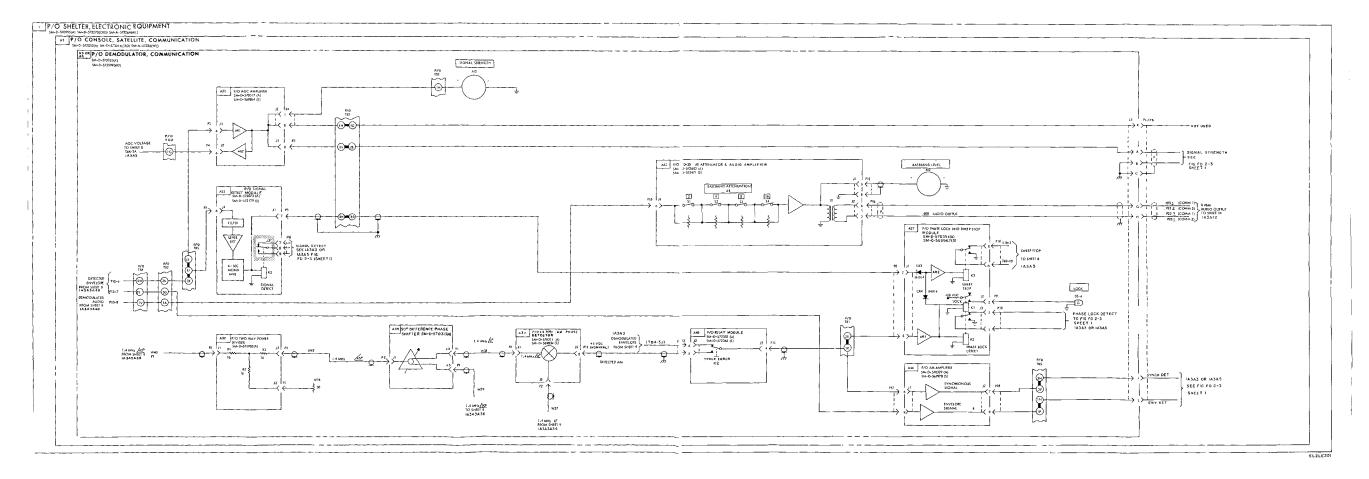

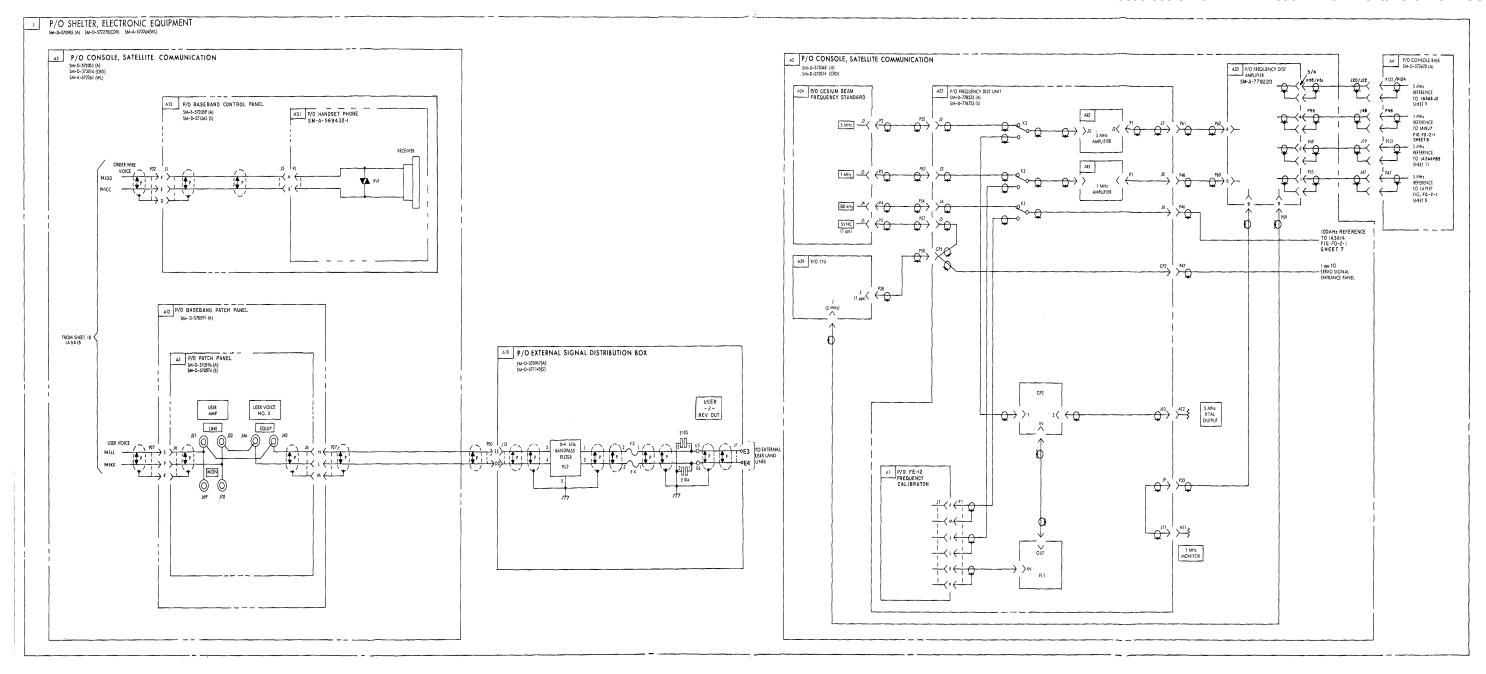

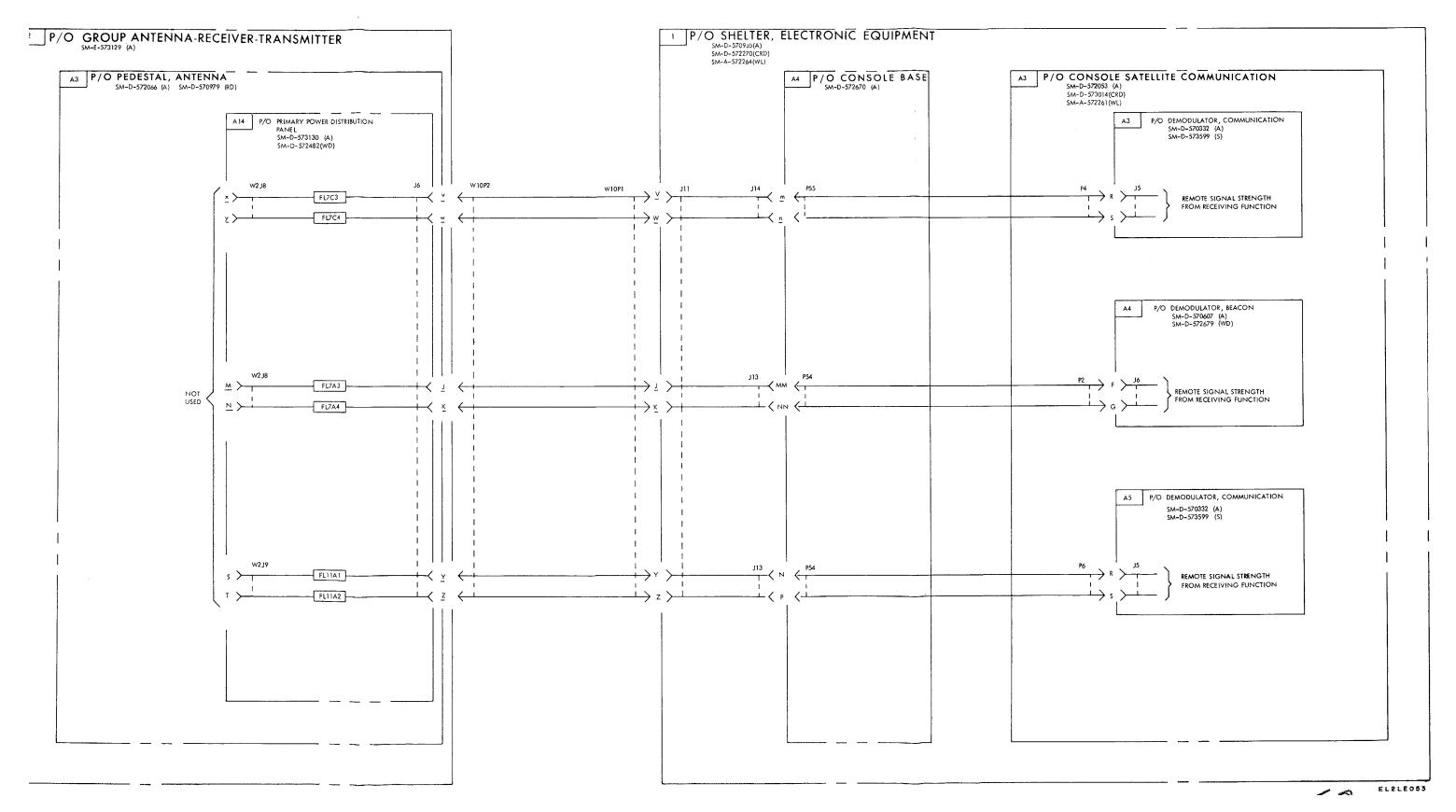

| FO 2-1 <sup>16</sup><br>FO 2-2'<br>the                                       | Satellite communication terminal AN/TSC-54, receiving function, signal flow diagram (19   | •               |               |

| through                                                                      |                                                                                           |                 | . manual      |

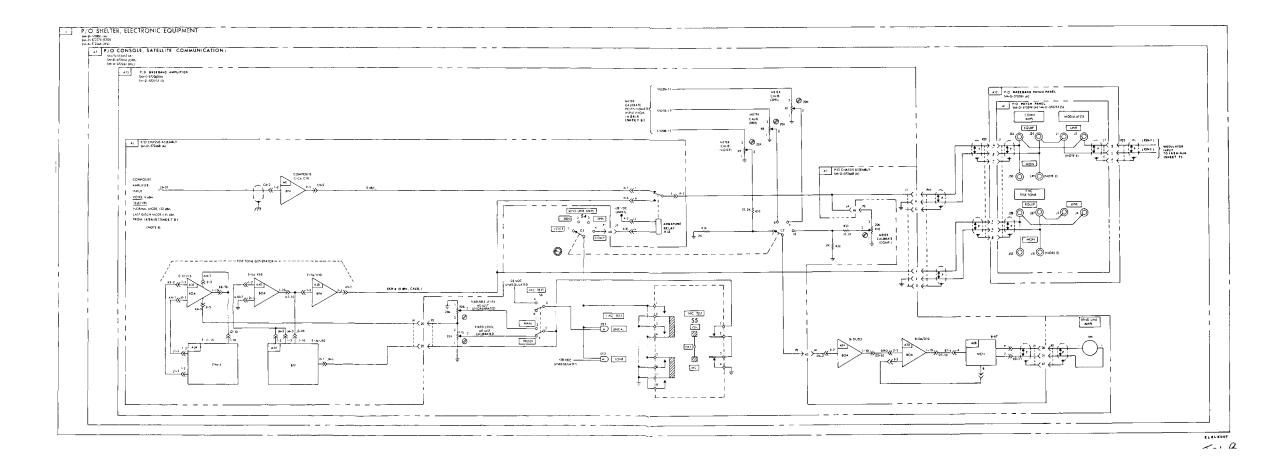

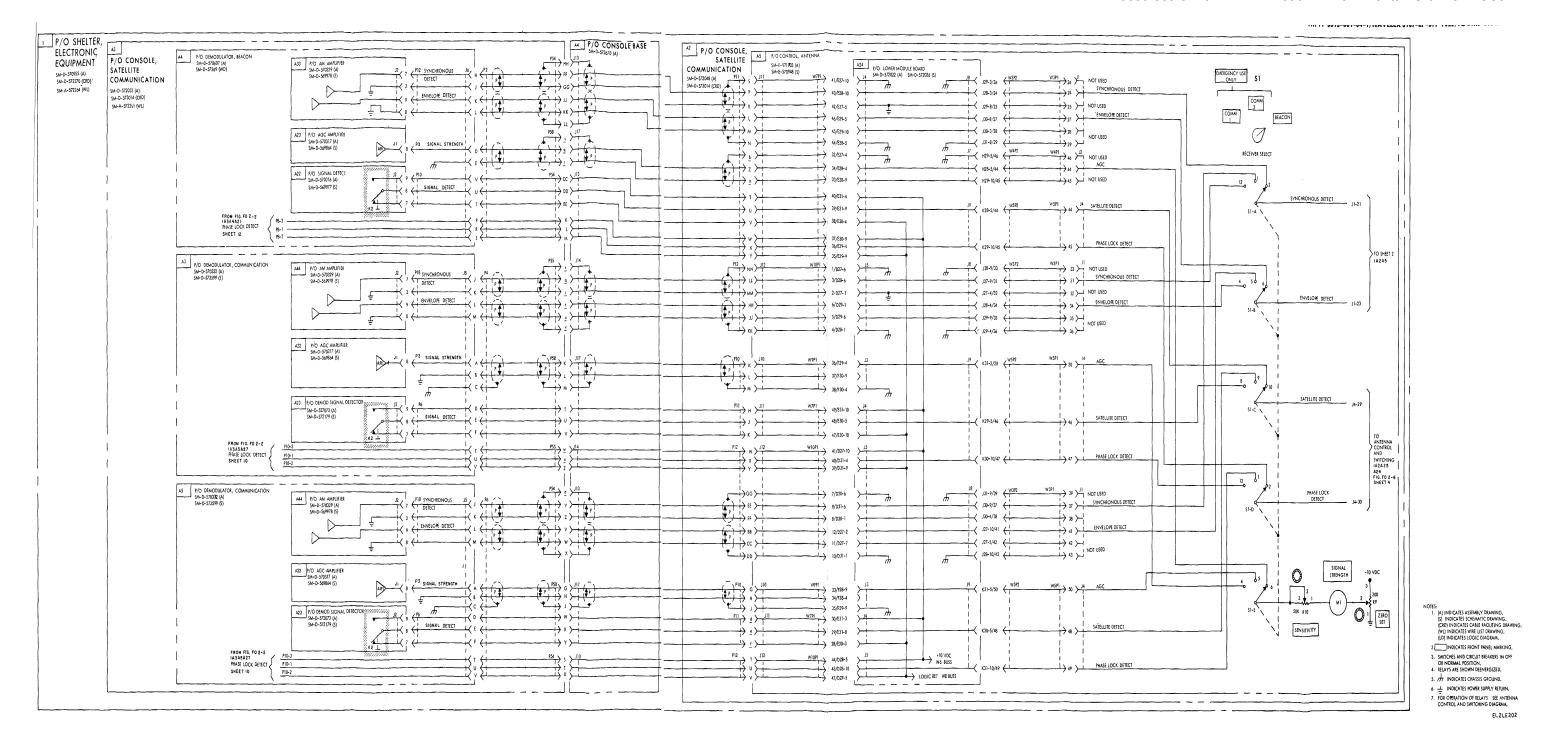

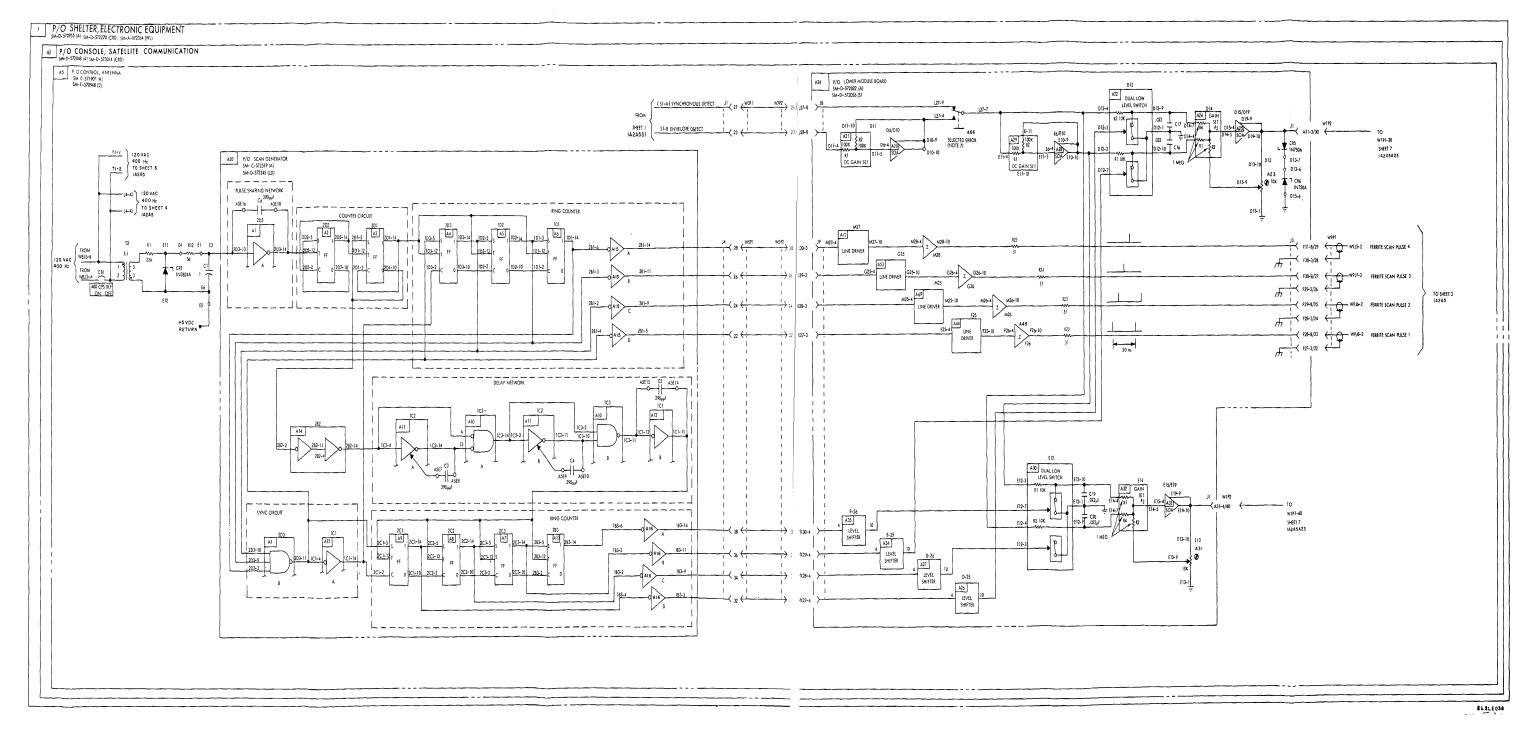

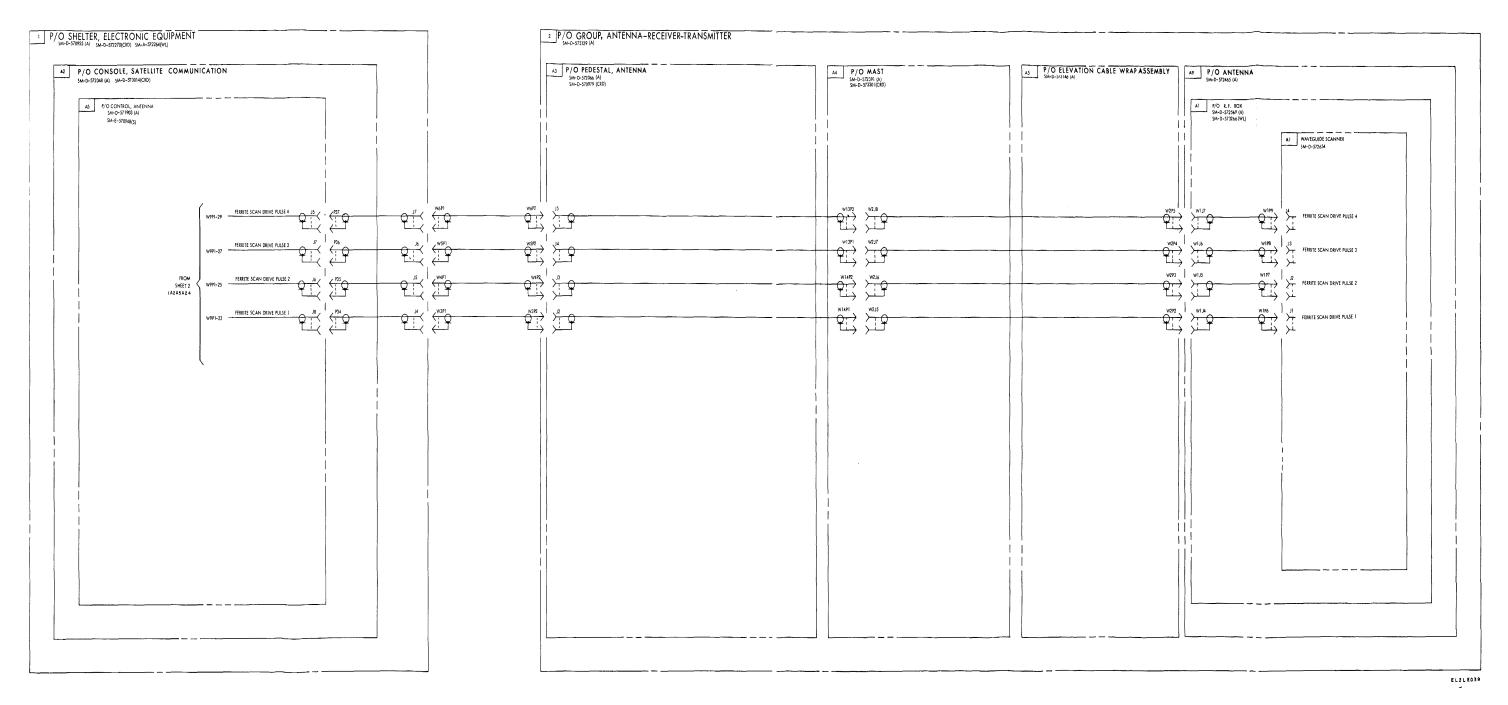

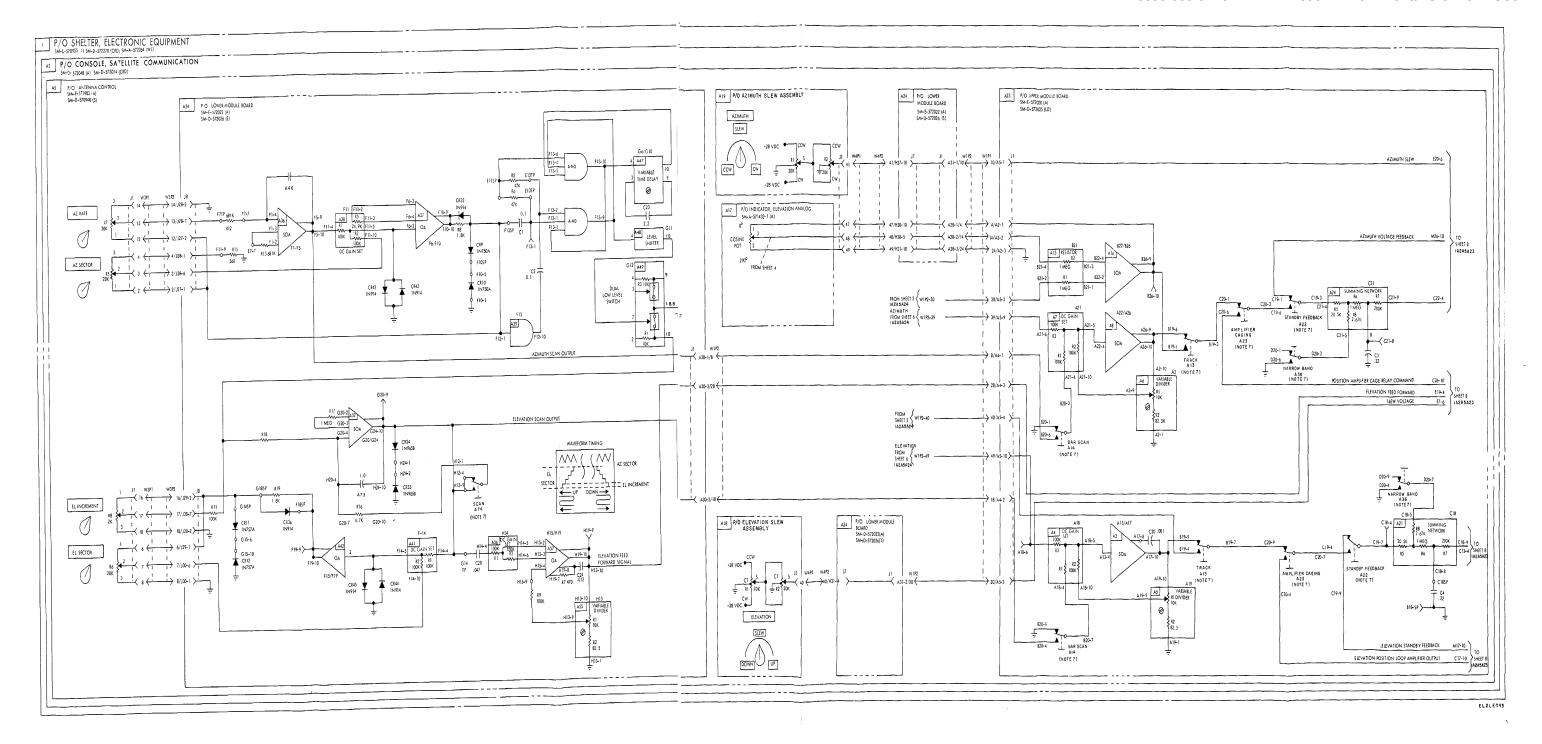

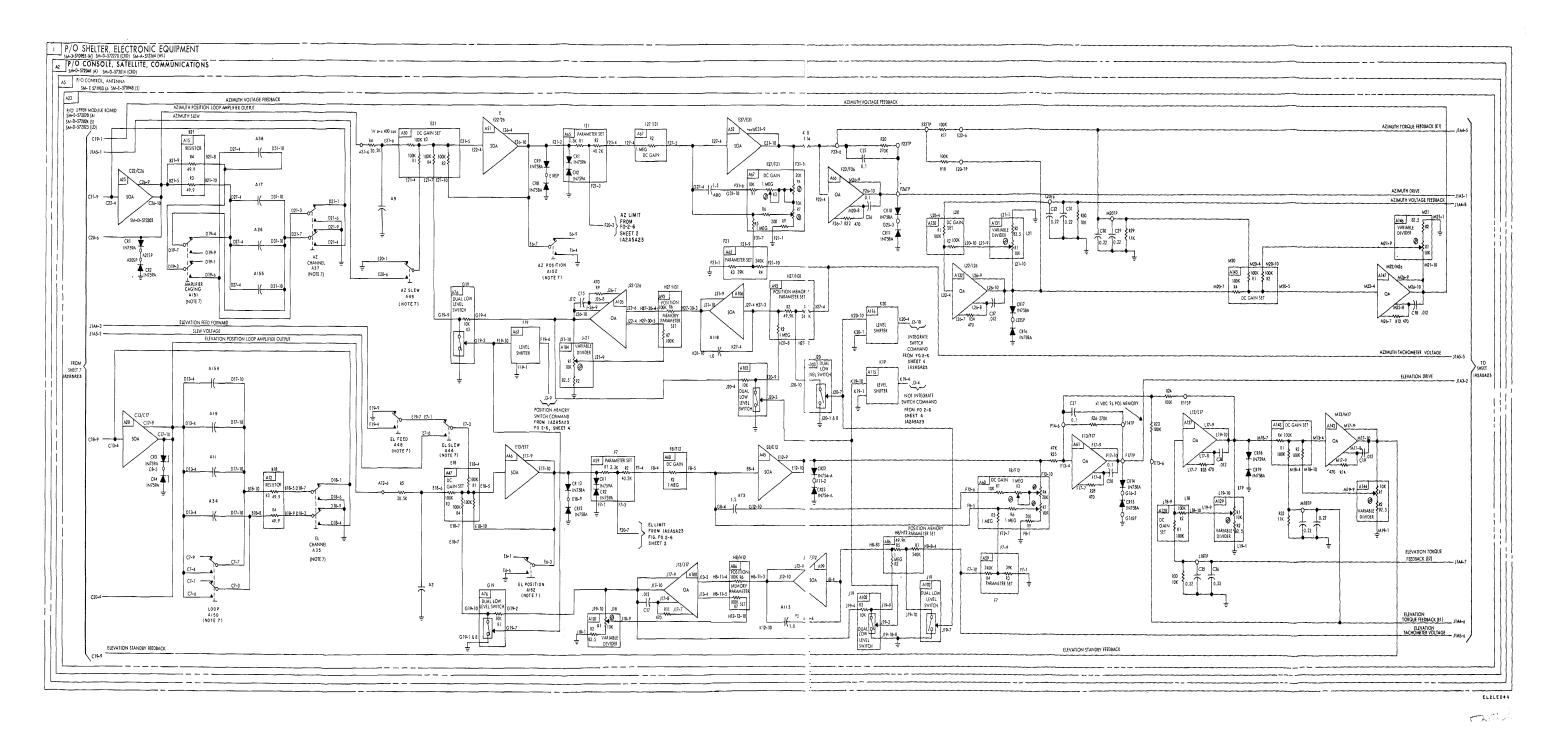

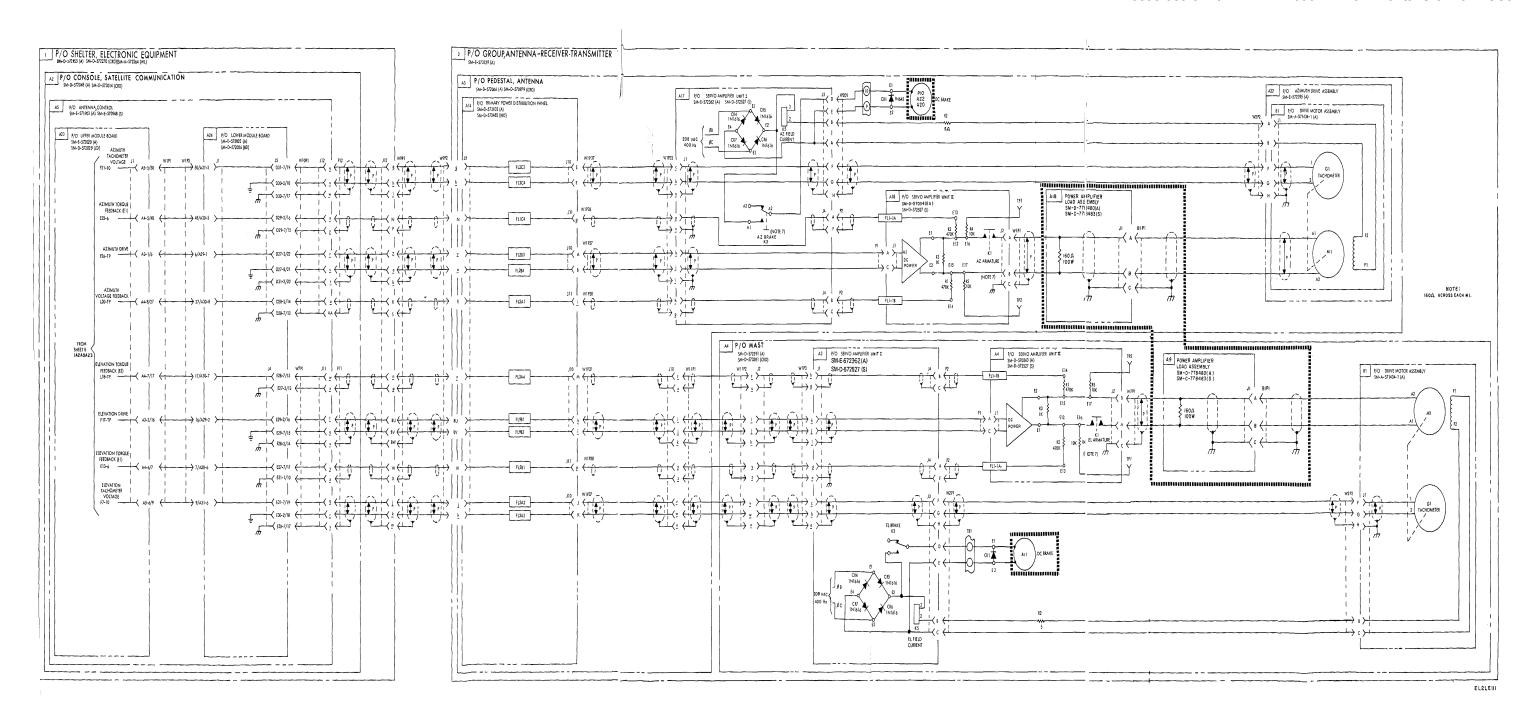

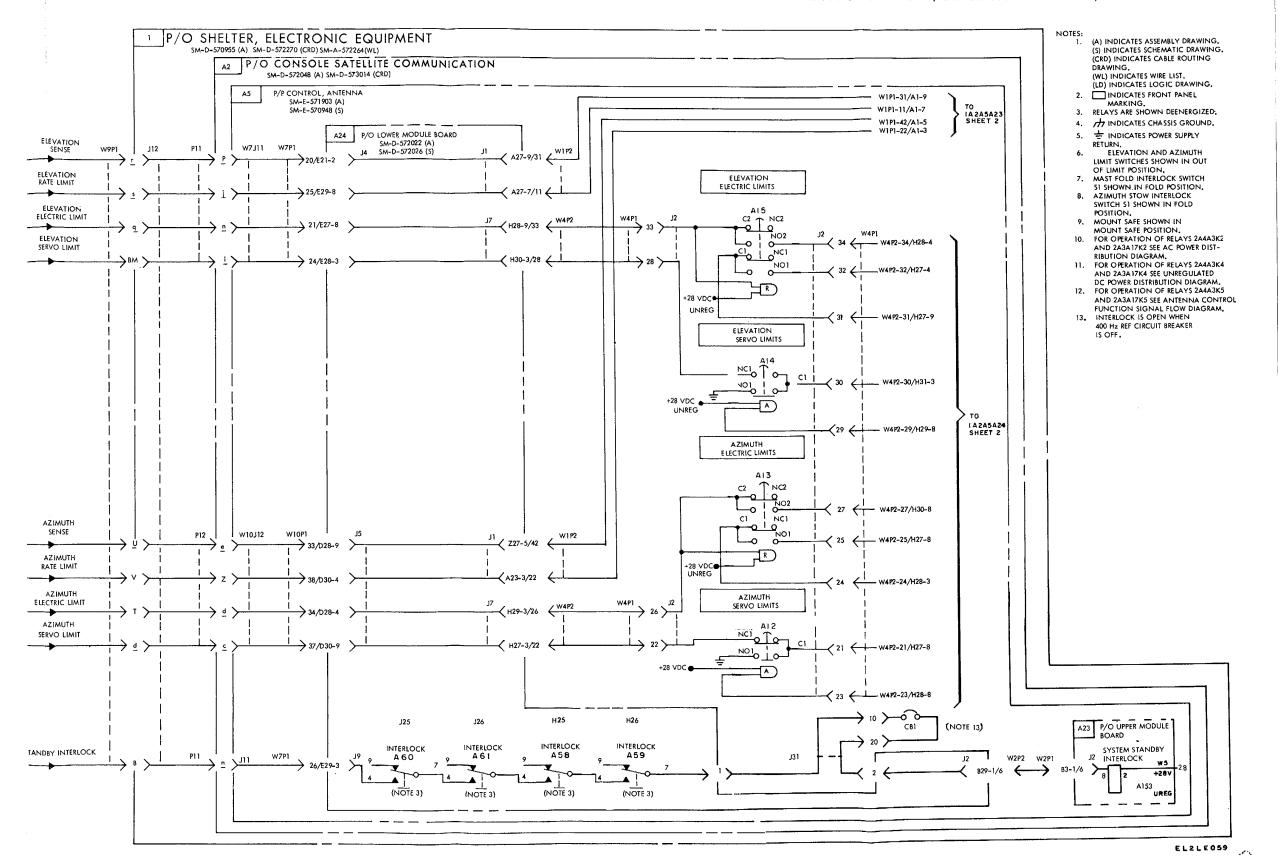

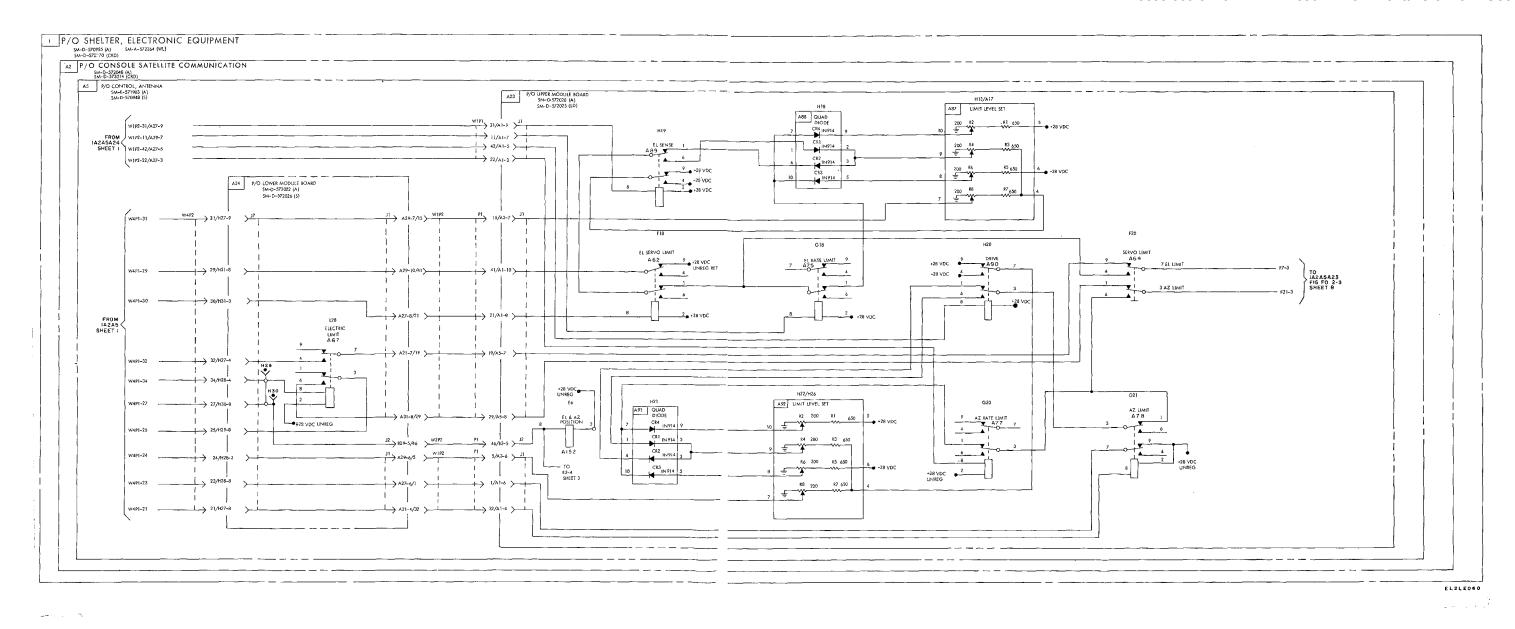

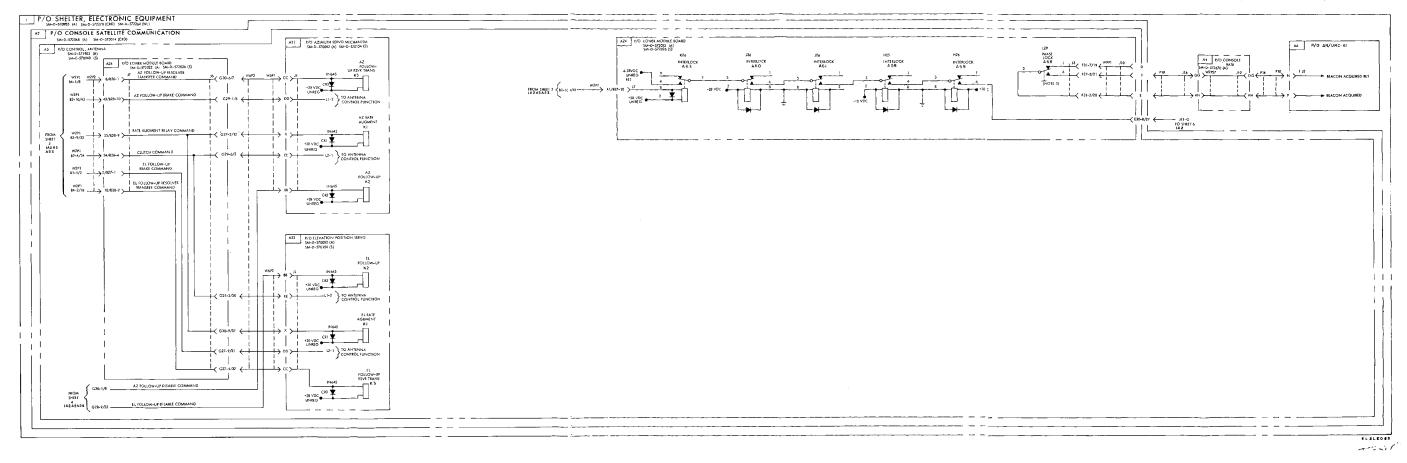

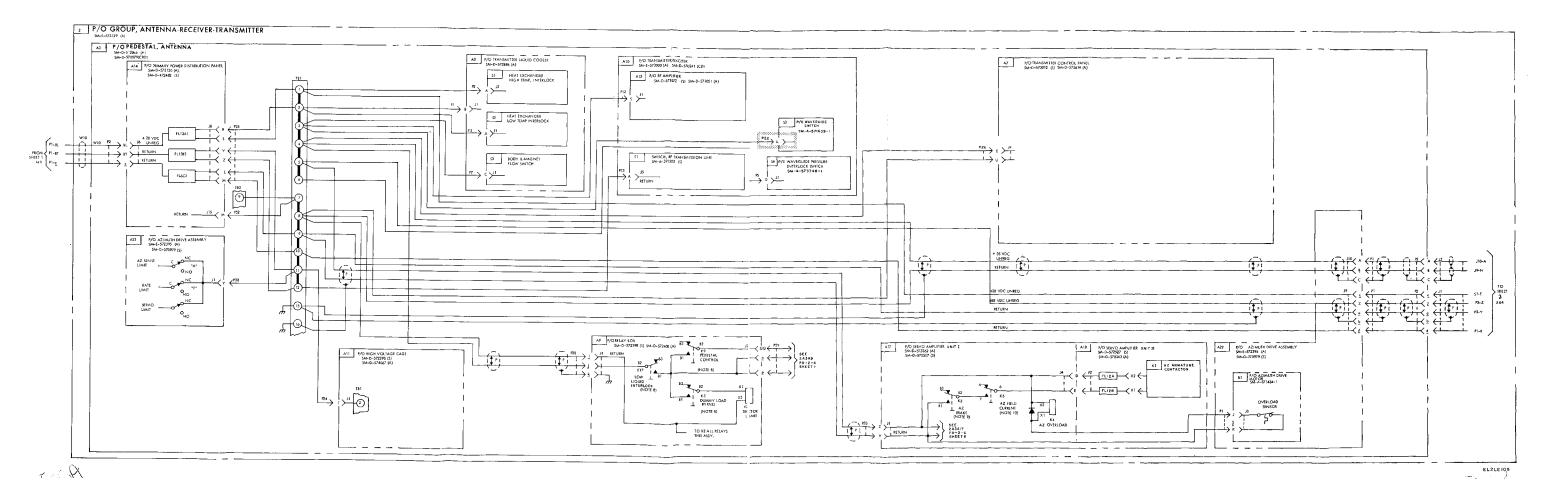

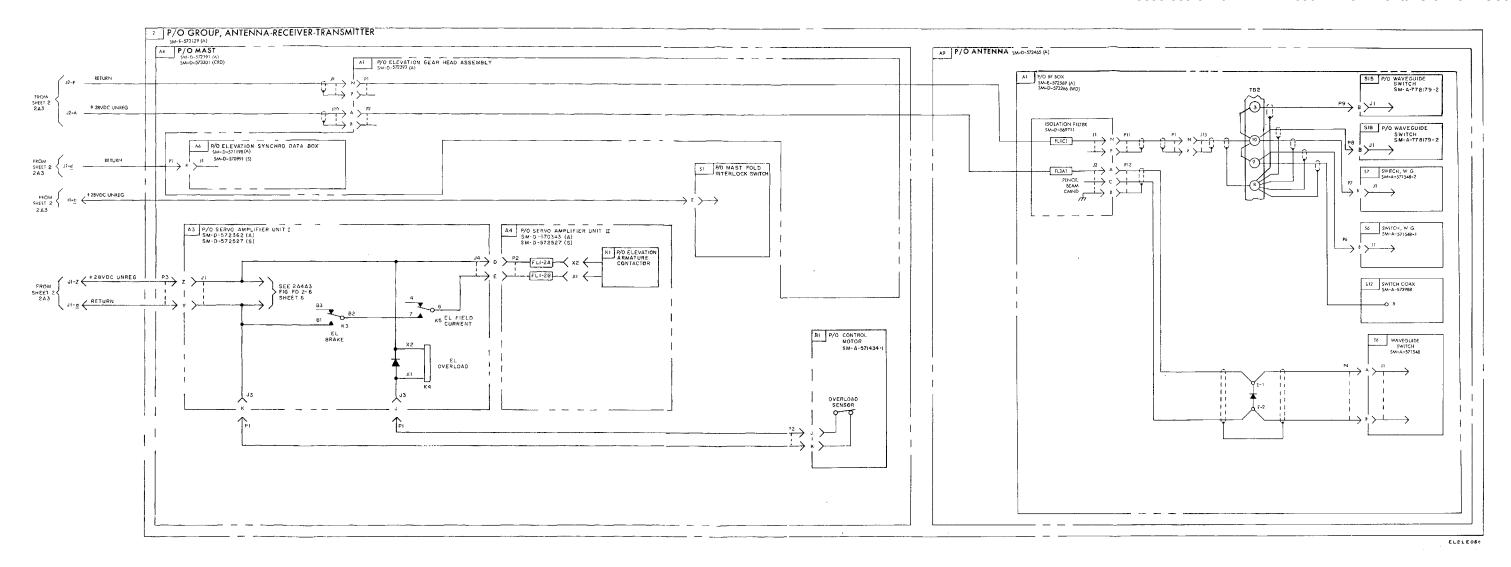

| FO 2-2 <sup>19</sup><br>FO 2-3 <sup>1</sup><br>through                       | Satellite communication terminal AN/TSC-54, antenna control function, signal flow diagram | am (9 sheets    | )             |

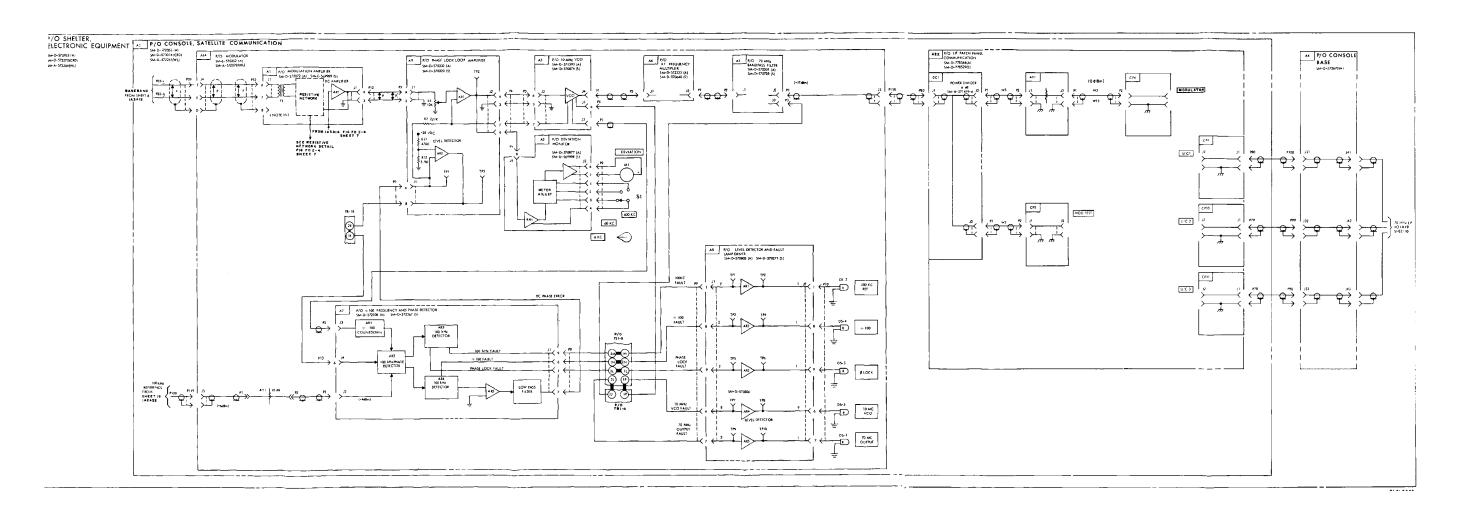

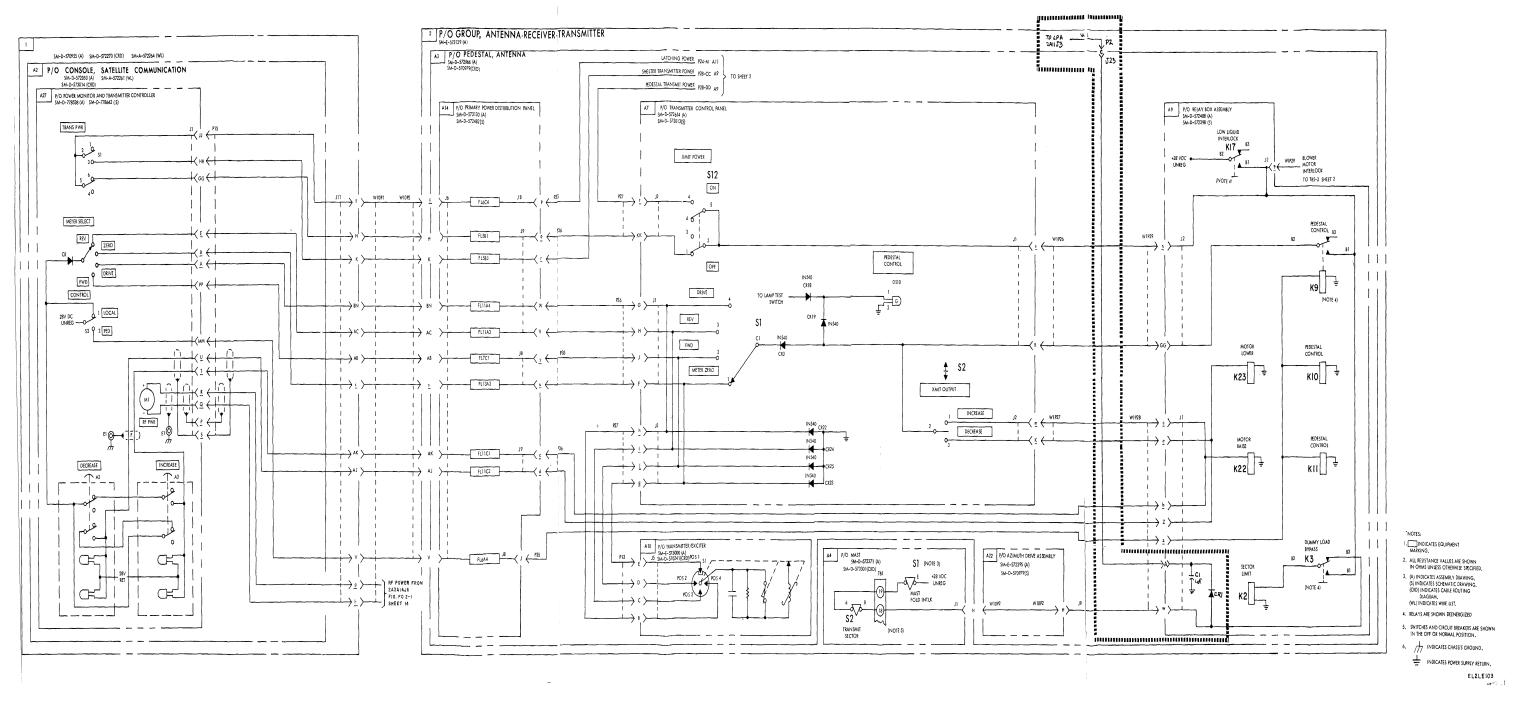

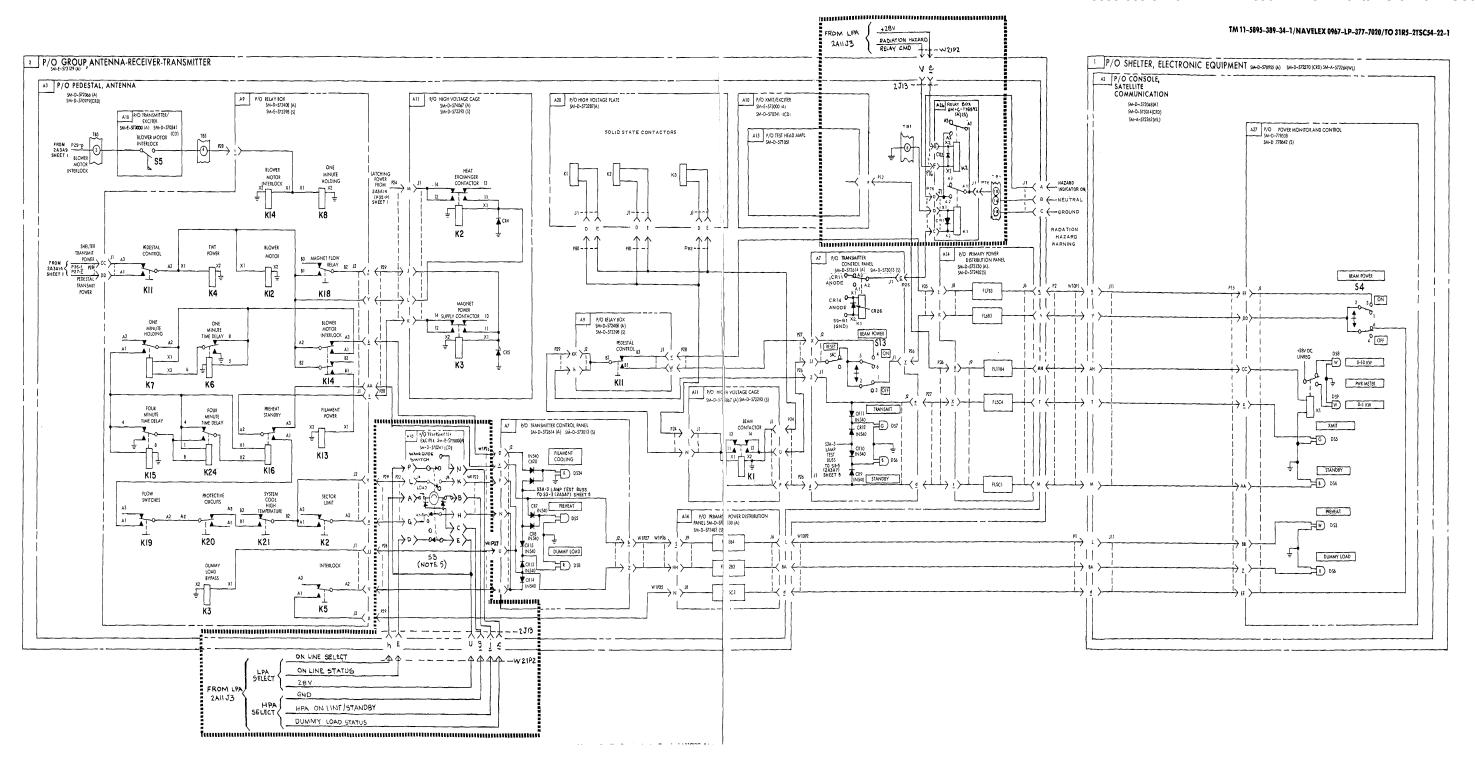

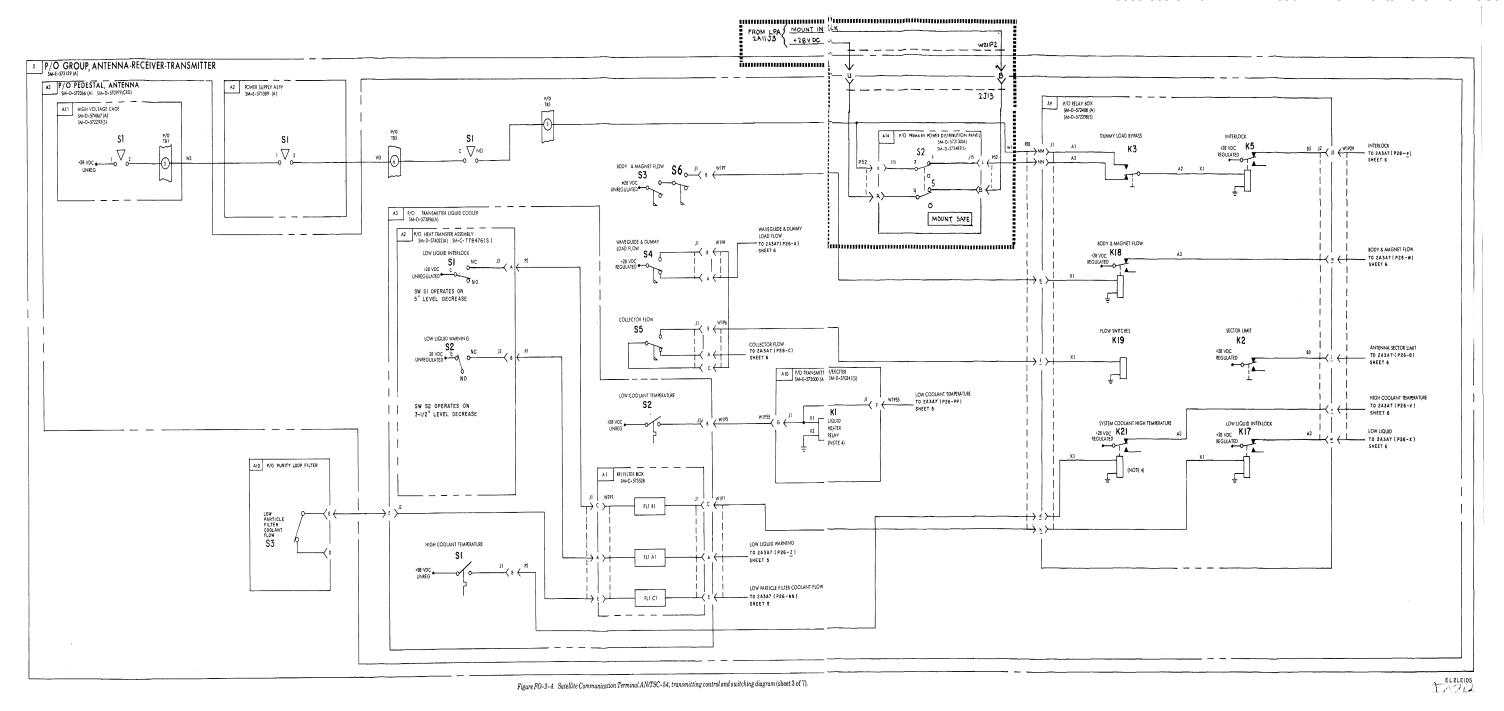

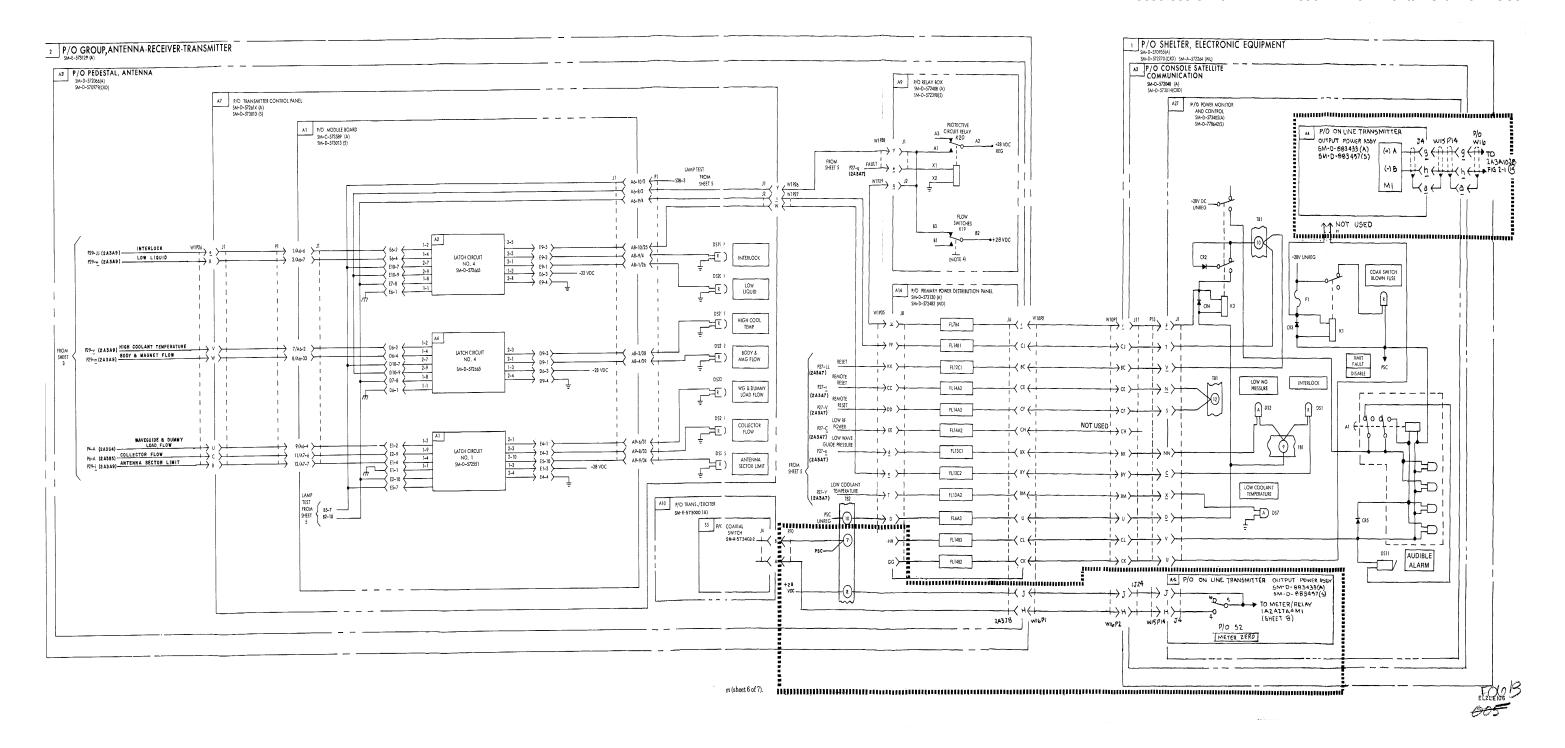

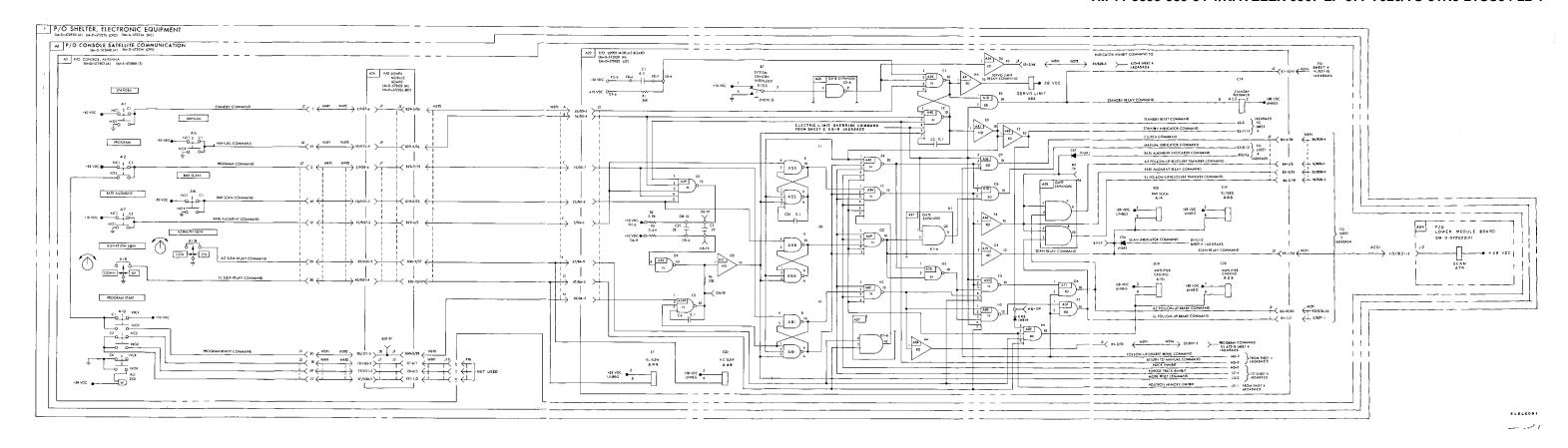

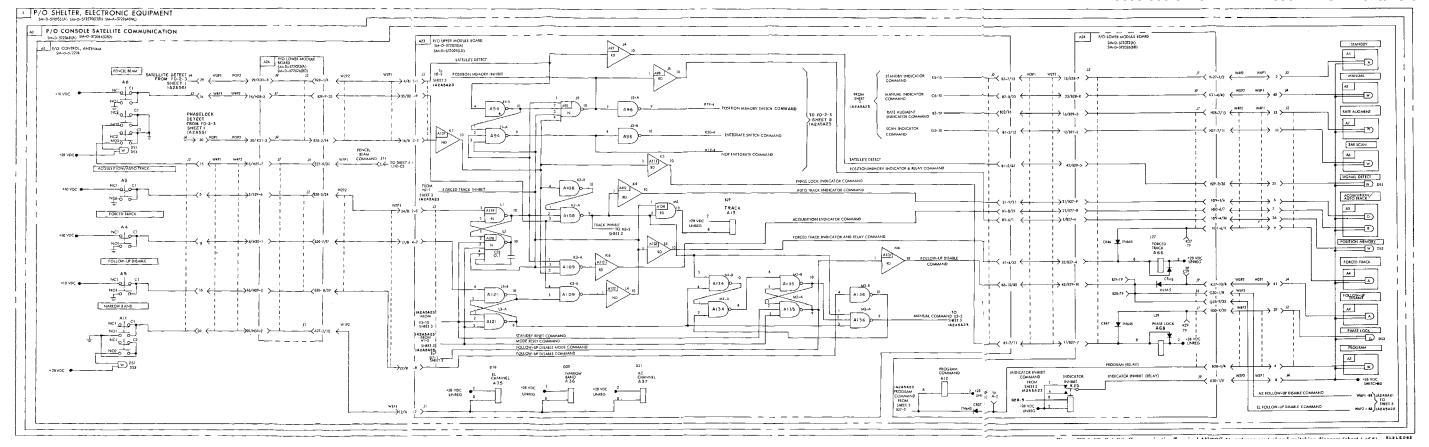

| FO 2-3 <sup>9</sup><br>FO 2-4 <sup>1</sup><br>through<br>FO 2-4 <sup>1</sup> | Satellite communication terminal AN/TSC-54, transmitting control and switching diagram    | n (7 sheets) .  |               |

<sup>\*</sup>This manual supersedes TM 11-5895-389-34/1, NAVSHIPS 0967-377-7020. TO 31R5-2TSC54-22, 12 February 1971 and TM 11-5895-389-34/3, NAVSHIPS 0967-377-7020, TO 31R5-2TSC54-22, 12 February 1971.

Change 1 i

## TM 11-589S-389--34-1/NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1

|   | Figure<br>Number                                                | Title                                                                                                                                                                                             | Page |

|---|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| ) | FO 02-4<br>FO 2-5 <sup>1</sup><br>through<br>FO2-5 <sup>6</sup> | Satellite communication terminal AN/TSC-54, transmitting control and switching diagram (sheet 7.1) Satellite communication terminal AN/TSC-54, receiving control and switching diagram (6 sheets) |      |

|   | FO 2-6 <sup>1</sup><br>through<br>FO2-6 <sup>1</sup>            | Satellite communication terminal AN/TSC-54, antenna control and switching diagram (6 sheets)                                                                                                      |      |

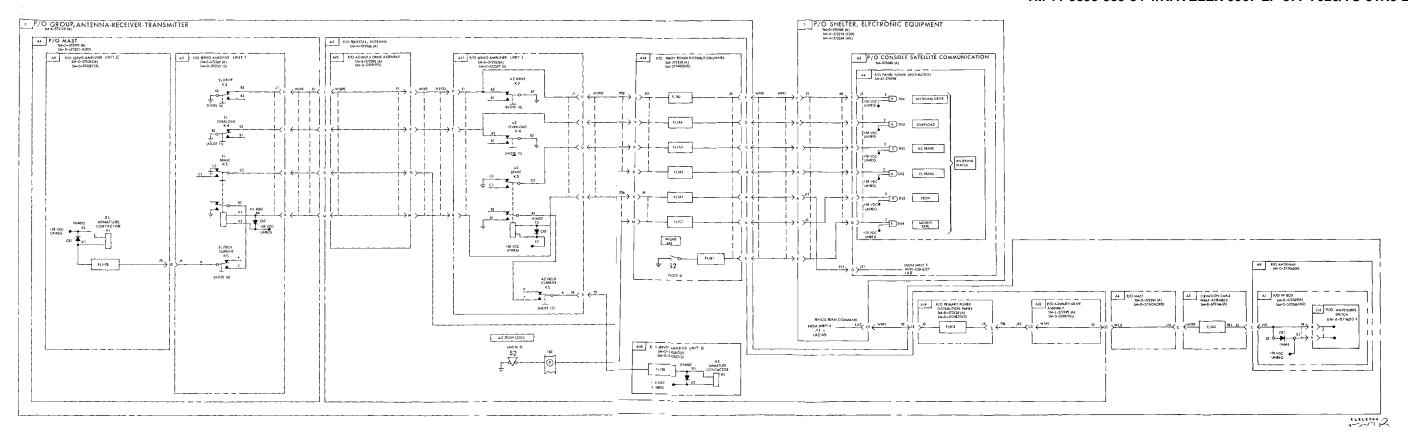

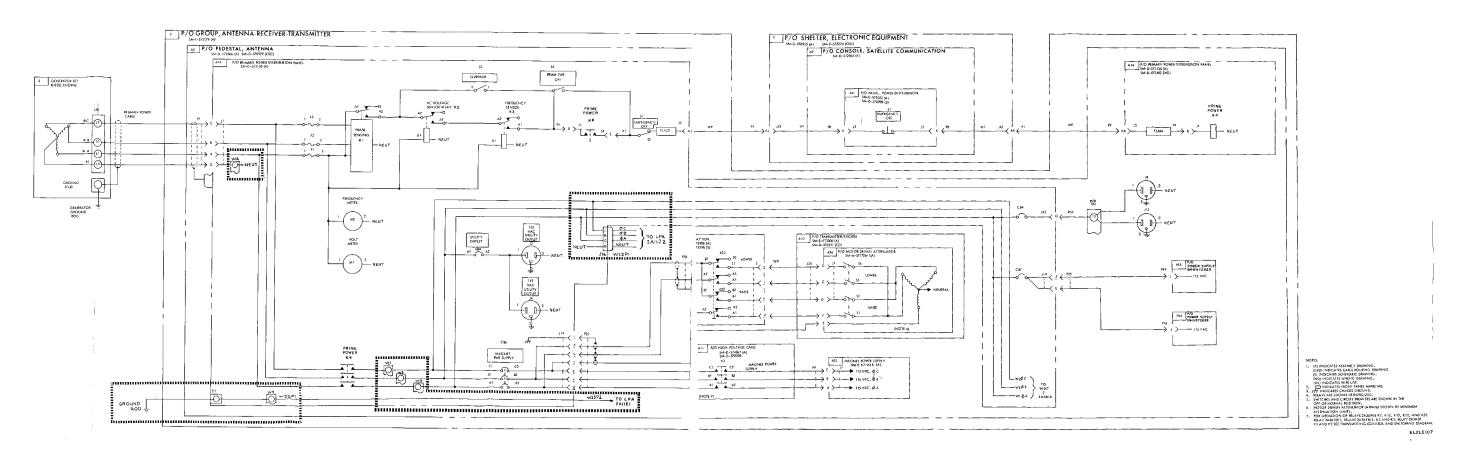

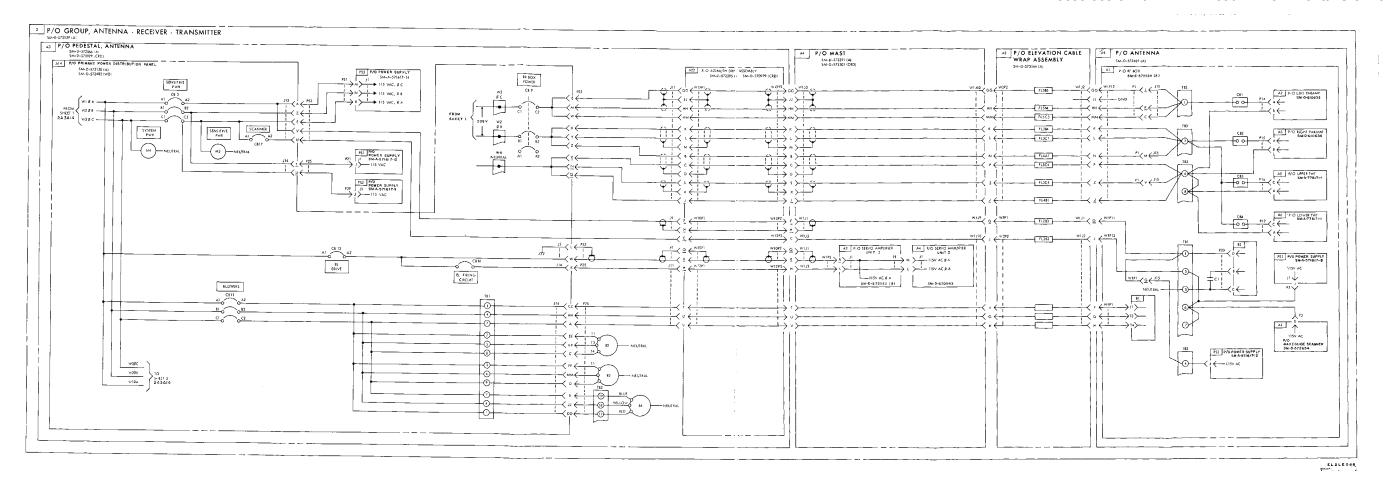

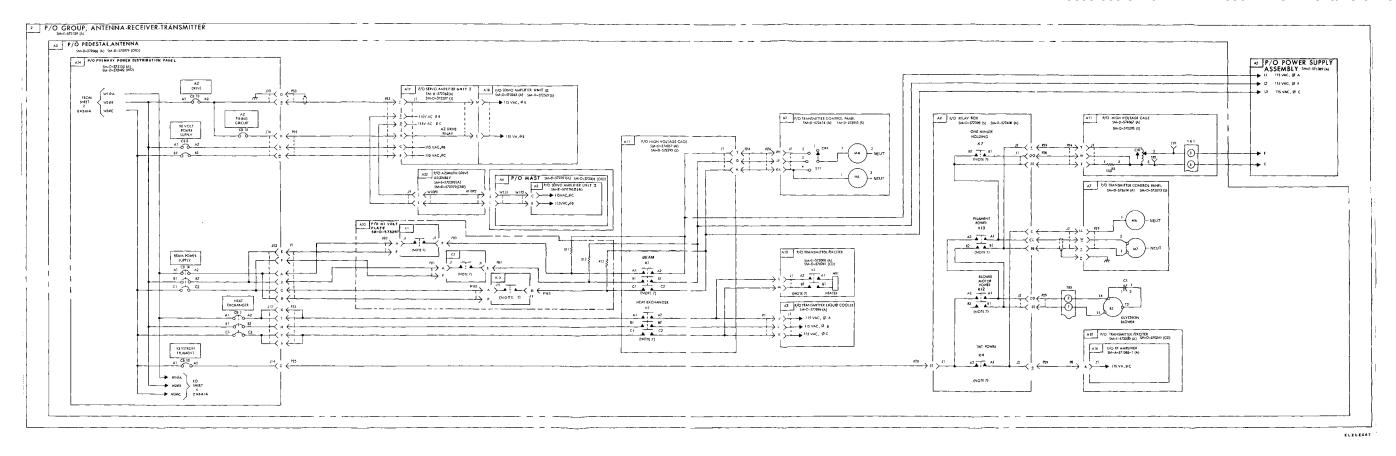

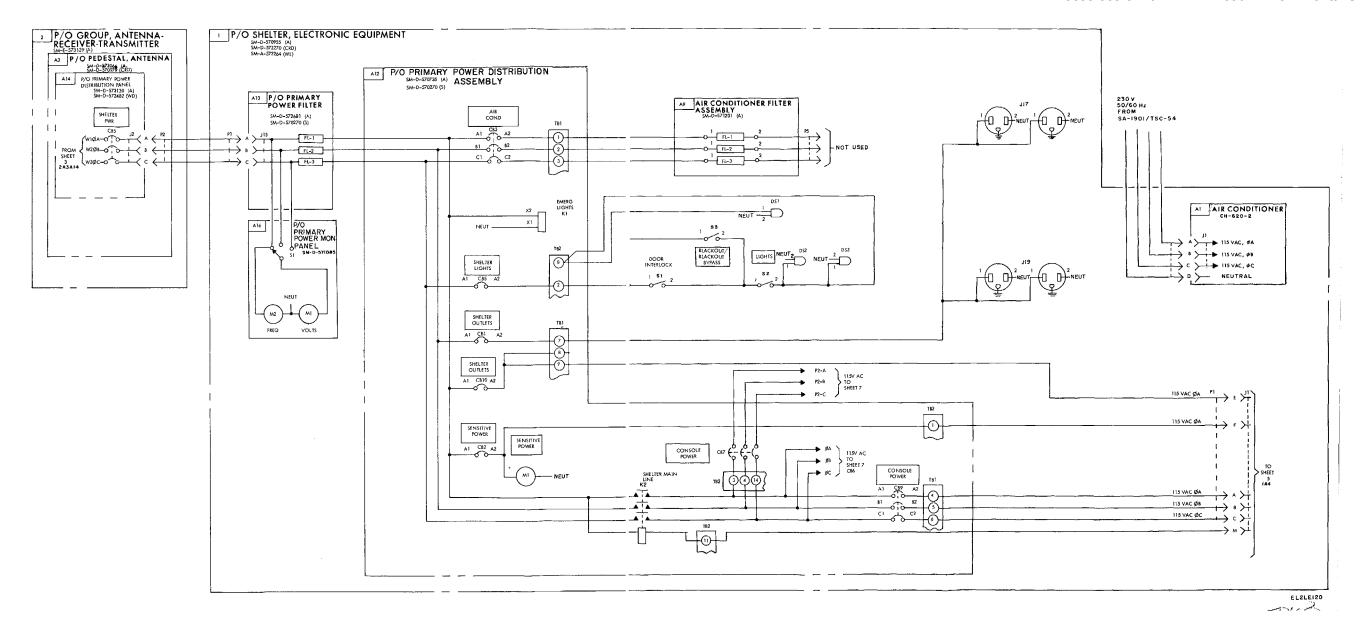

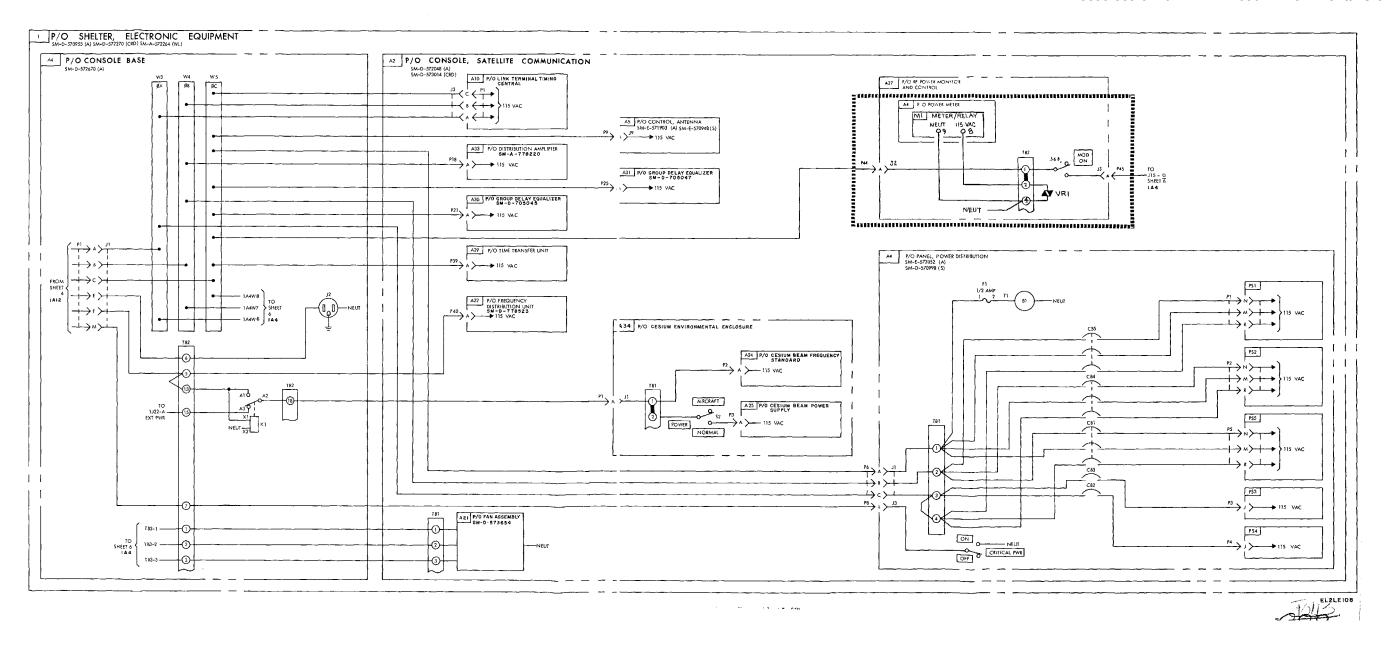

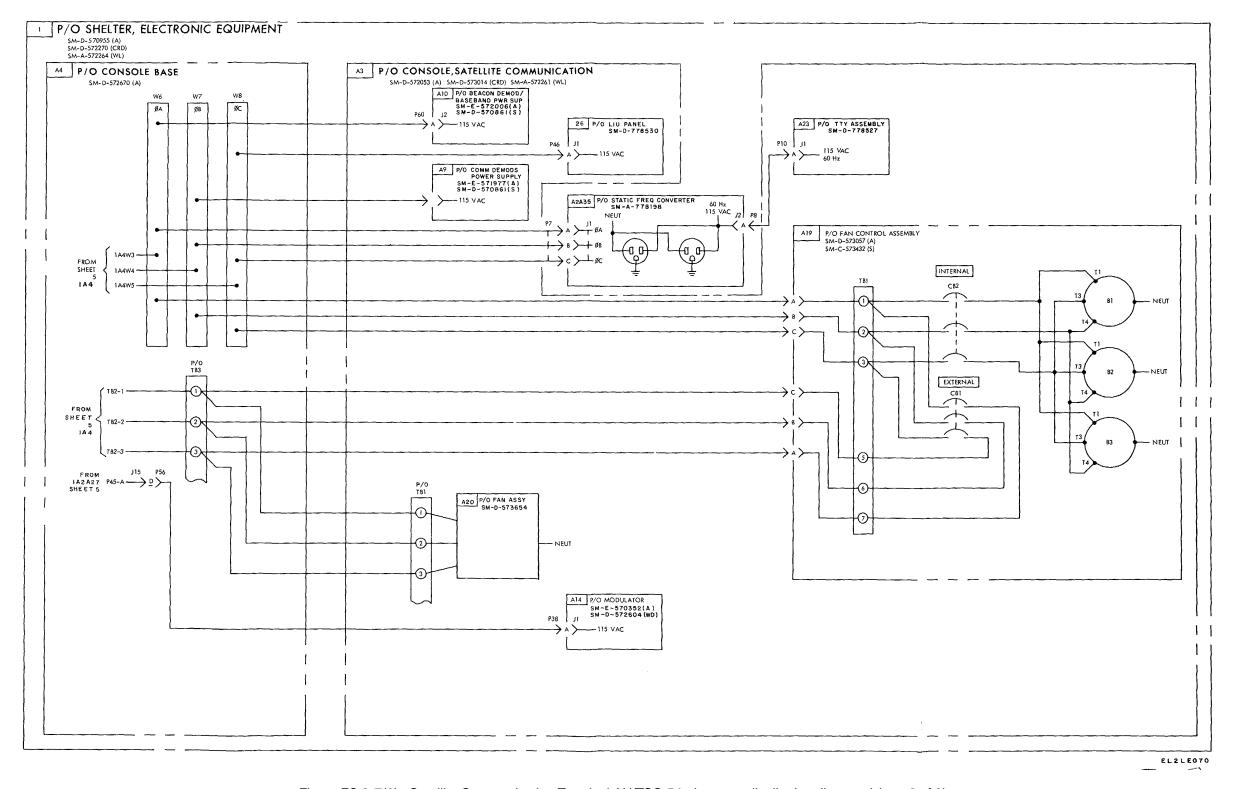

|   | FO 2-7 <sup>1</sup><br>through<br>F02-7 <sup>9</sup>            | Satellite communication terminal AN/TSC-54, ac power distribution diagram (9 sheets)                                                                                                              |      |

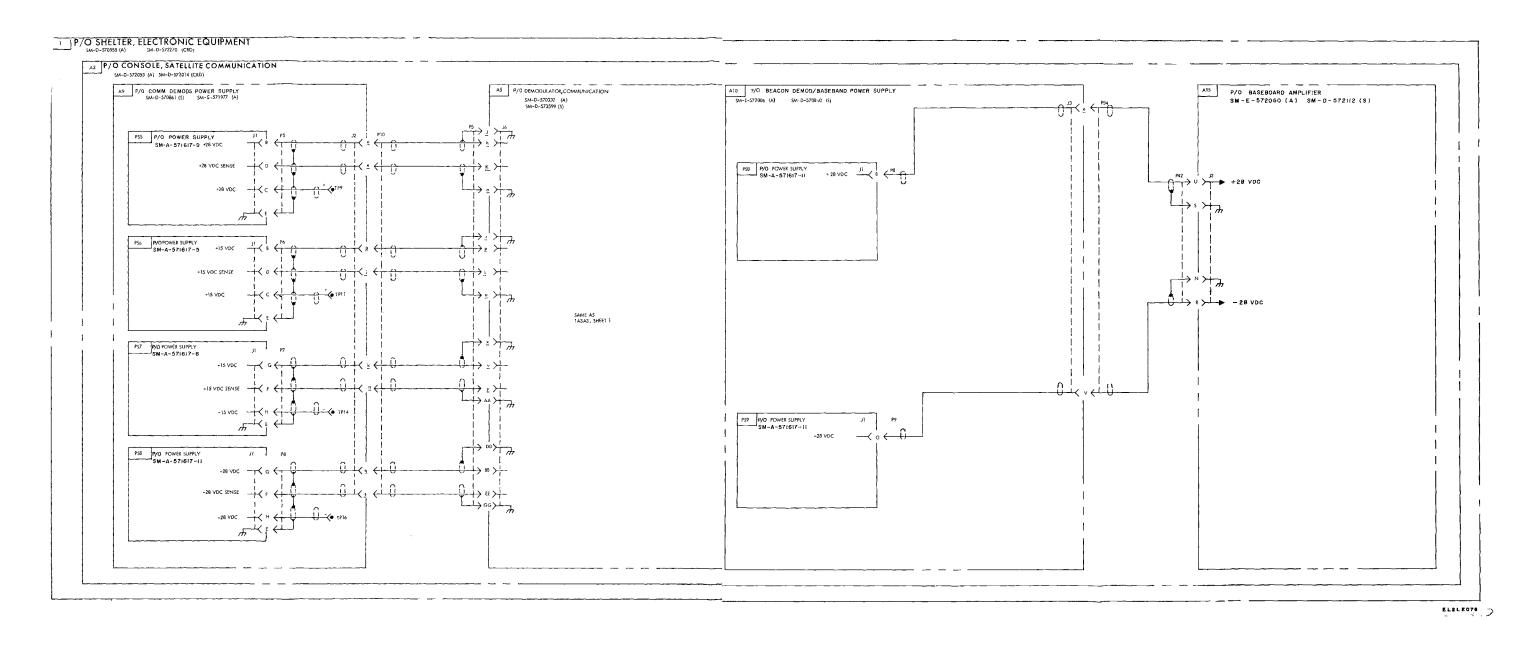

|   | FO 2-8 <sup>1</sup><br>through<br>FO 2-8 <sup>10</sup>          | Satellite communication terminal A NTSC-54, regulated dc power distribution diagram (10 sheets)                                                                                                   |      |

|   | FO 2-9 <sup>1</sup><br>through<br>FO 2-9 <sup>2</sup>           | Satellite communication terminal ANITSC-54, unregulated dc power distribution diagram (3 sheets)                                                                                                  |      |

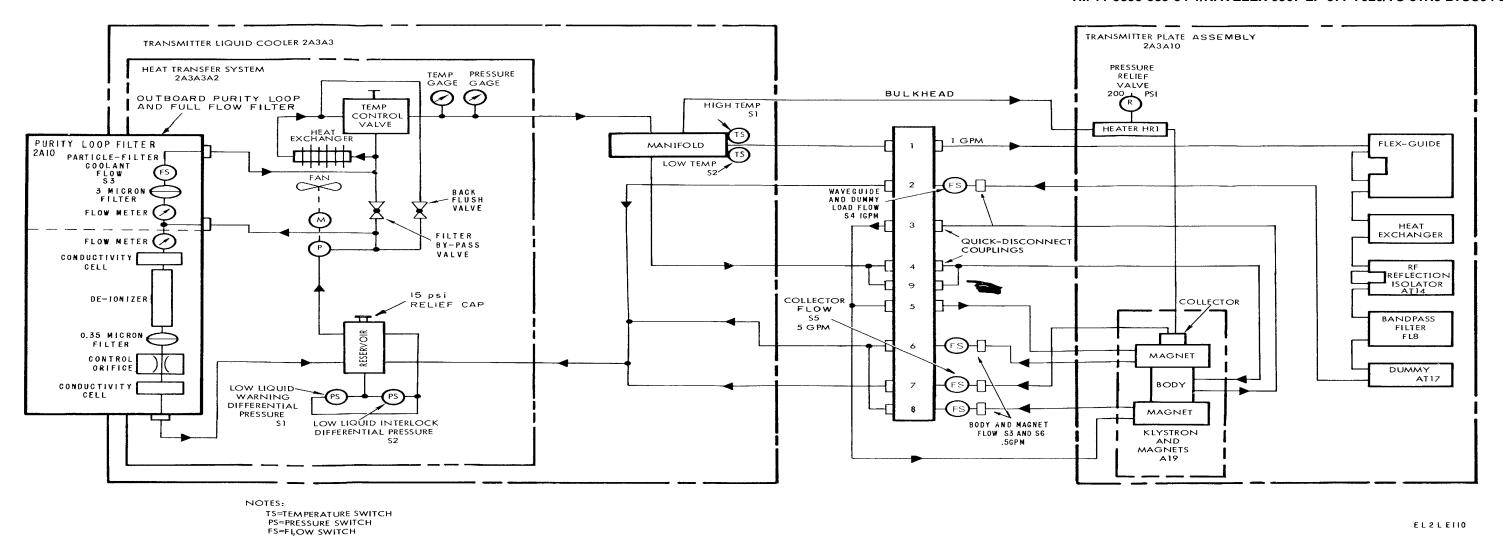

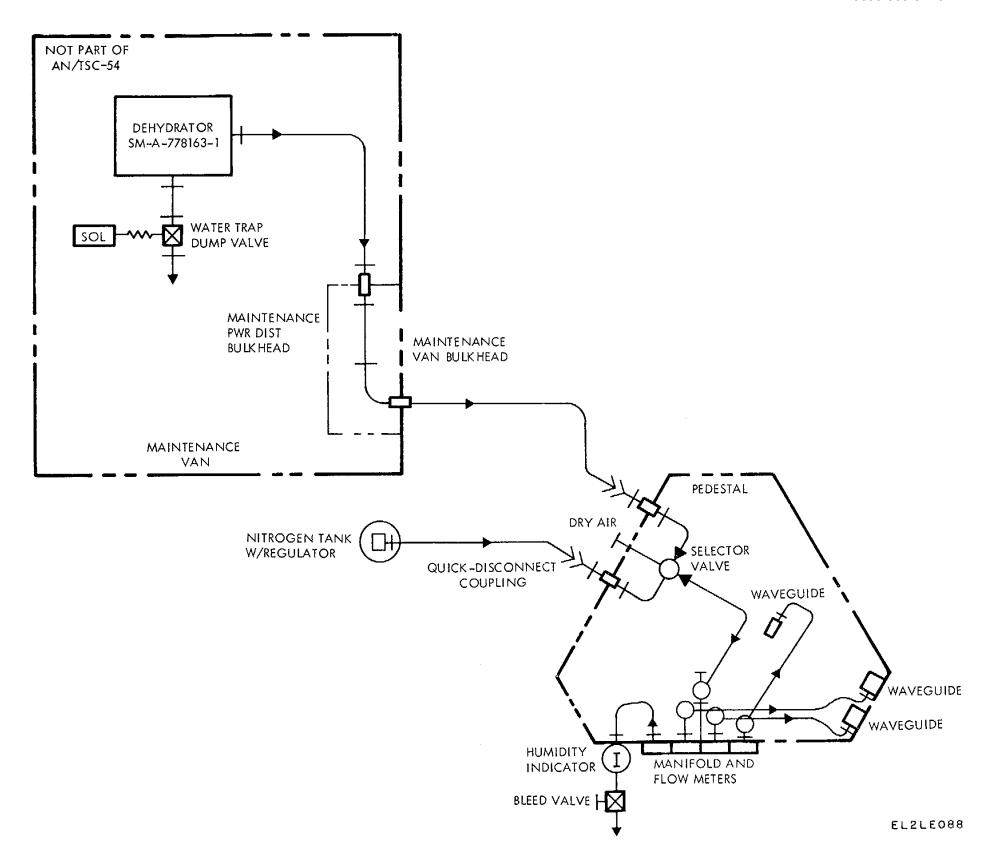

|   | FO 2-10<br>FO 2-11<br>FO 2-12                                   | Transmitter cooling system, flow diagram  Waveguide pressurization system, flow diagram  Satellite communication terminal ANITSC- 54, intercom system diagram.                                    |      |

Change 1 ii

## CHAPTER 1 INTRODUCTION

#### Section I. GENERAL

#### 1-1. Scope

- a. This manual contains instructions for direct support and general support maintenance of Satellite Communication Terminal AN/TSC54. It includes instructions for troubleshooting, testing, alignment, repairing the equipment, and replacing specific maintenance parts. It also lists the tools, materials, and test equipment required for direct and general support maintenance.

- b. The manual consists of three volumes. TM 11-5895-389-34-1 contains a functional analysis of the equipment operation and the illustrations to support this functional analysis of the equipment operation and the illustrations to support this functional analysis. TM 11-5895-389-34-2 contains a detailed circuit analysis of the equipment and the illustrations to support the detailed circuit analysis. TM 11-5895-389-34-3 contains preventive maintenance information, troubleshooting data, removal and replacement instructions, alignment procedures, general support testing information, and the index for the complete manual.

#### 1-2. Forms and Records

a. Reports of Maintenance and Unsatisfactory Equipment. Maintenance forms, records, and reports which are to be used by maintenance personnel at all maintenance levels are listed in and prescribed by TM 38-750 (Army). Air Force personnel will use AFM 66-1 for maintenance reporting and TO-00-35D54 for unsatisfactory equipment reporting. Navy personnel will report maintenance performance utilizing the

Maintenance Data Collection Subsystem (MDCS) IAW OPNAVINST 4790.2, Vol. 3 and unsatisfactory material/conditions (UR submissions) IAW OPNAVINST 4790.2, Vol. 2, chapter 17.

- b. Report of Packaging and Hang Deficiencies. Fill out and forward DD Form 6 (Packaging Improvement Report) as prescribed in AR 700-58/NAVSUPINST 4030.29/AFR 7113/MCO P4030.29A, and DLAR 4145.8.

- c. Discrepancy in Shipment Report (DISREP) (SF 361). Fill out and forward Discrepancy in Shipment Report (DISREP) (SF 361) as prescribed in AR 55-38/NAVSUPTNST 4610.33B/AFR 75-18/MCO P4610.19C, and DLAR 4500.15.

#### 1-3. Administrative Storage

Administrative storage instructions are provided in TM 740-90-1.

#### 1-4. Destruction of Army Electronics Materiel

Demolition and destruction of electronic equipment will be under the direction of the commander and in accordance with TM 750-244-2.

## 1-5. Reporting Equipment Improvement Recommendations (EIR)

EIR's will be prepared using DA Form 2407 (Maintenance Request). Instructions for preparing EIR's are provided in TM 38-750, The Army Maintenance Management System. EIR's should be mailed direct to Commander, US Army Electronics Command, ATTN: DRSELMA-, Fort Monmouth, NJ 07703. A reply will be furnished direct to you.

#### Section II. DESCRIPTION AND DATA

#### 1-6. Description

A description of components for the AN/TSC-54 is provided in TM 11-5895-389-12.

#### 1-7. Equipment Analysis

a. To simplify theoretical discussion, the AN/TSC 54 has been divided into five basic component groups

or systems: the transmitting system, the receiving system, the antenna control system, the control circuits system, and the power distribution system.

b. General theory of the AN/TSC-54 is

covered in a block diagram analysis (para 1-8) and detailed theory of the major assemblies is covered in a functional diagram analysis (para 2-4 through 2-76). Selected individual circuit subassemblies and modules are analyzed schematically in TM 11-5895-389-34-2.

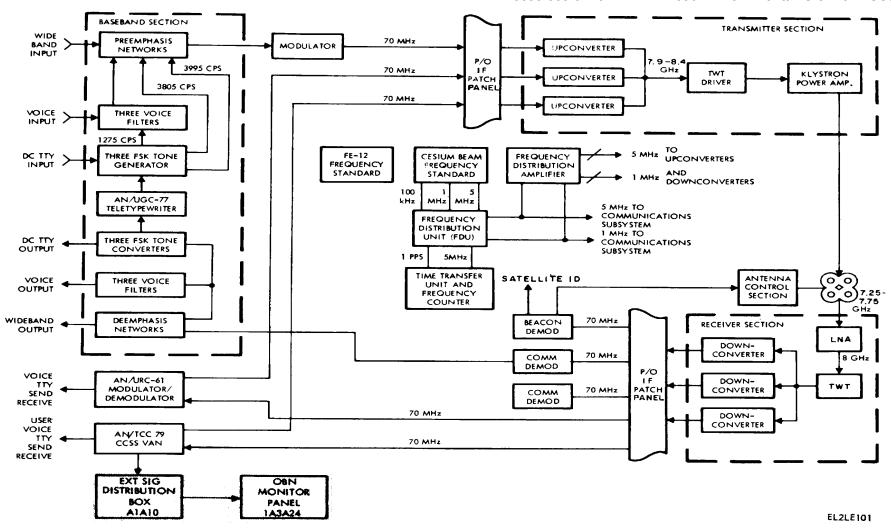

## 1-8. Block Diagram Analysis

(fig. 1-1)

The AN/TSC-54 is a transportable microwave communications link terminal incorporating all ancillary items necessary for operation through satellites to other link terminals configured to the same communication The AN/TSC-54 is capable of satellite system. simultaneous transmission of two wideband carrier signals. The AN/TSC-54 provides a communication capacity of one voice circuit, and one out-of-band 100 word-per-minute (wpm) full duplex teletypewriter orderwire circuit. Multiple access and antijamming capabilities are provided by radio Communication Subsystem AN/URC-61. User service of the AN/TSC-54 is provided by local loops or by interconnection to distribution points through microwave or transmission lines. When the AN/TSC-54 is used Communications Subsystem AN/TCC-79,, link terminal capabilities are increased by providing a maximum of 72 multiplex channels for transmission through the AN/TSC-54.

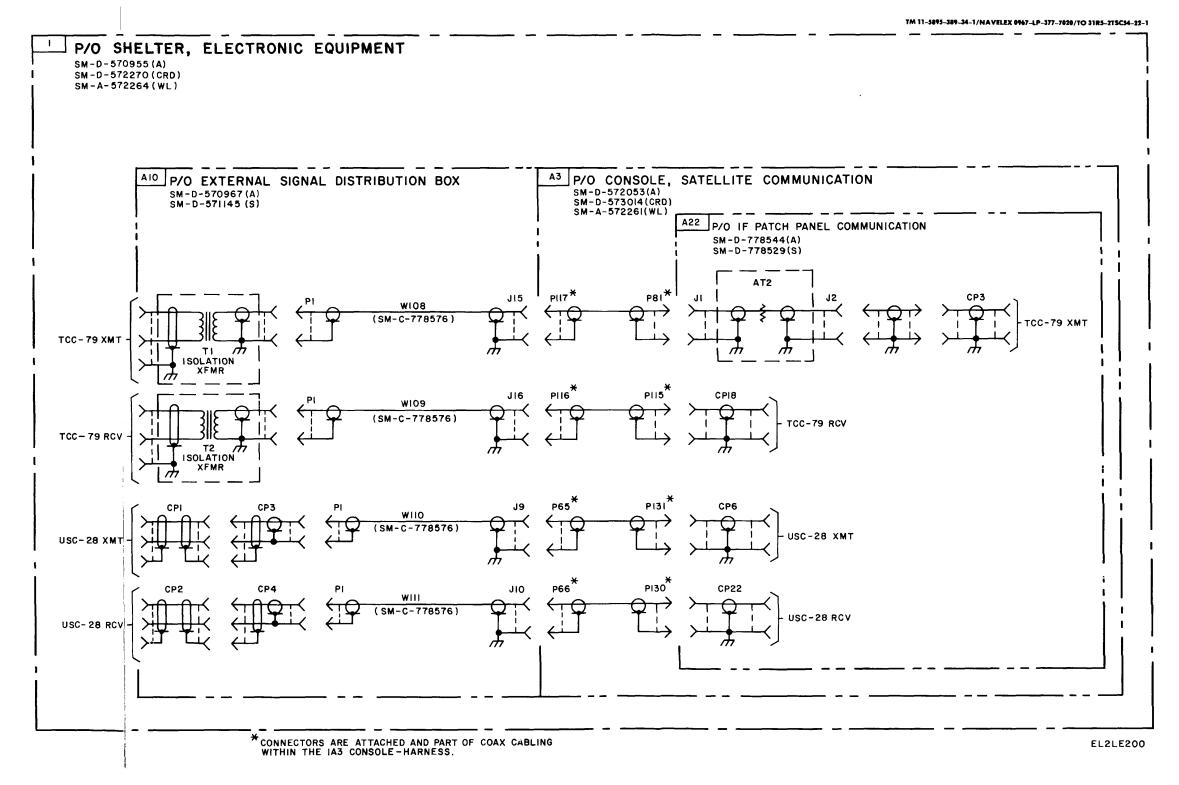

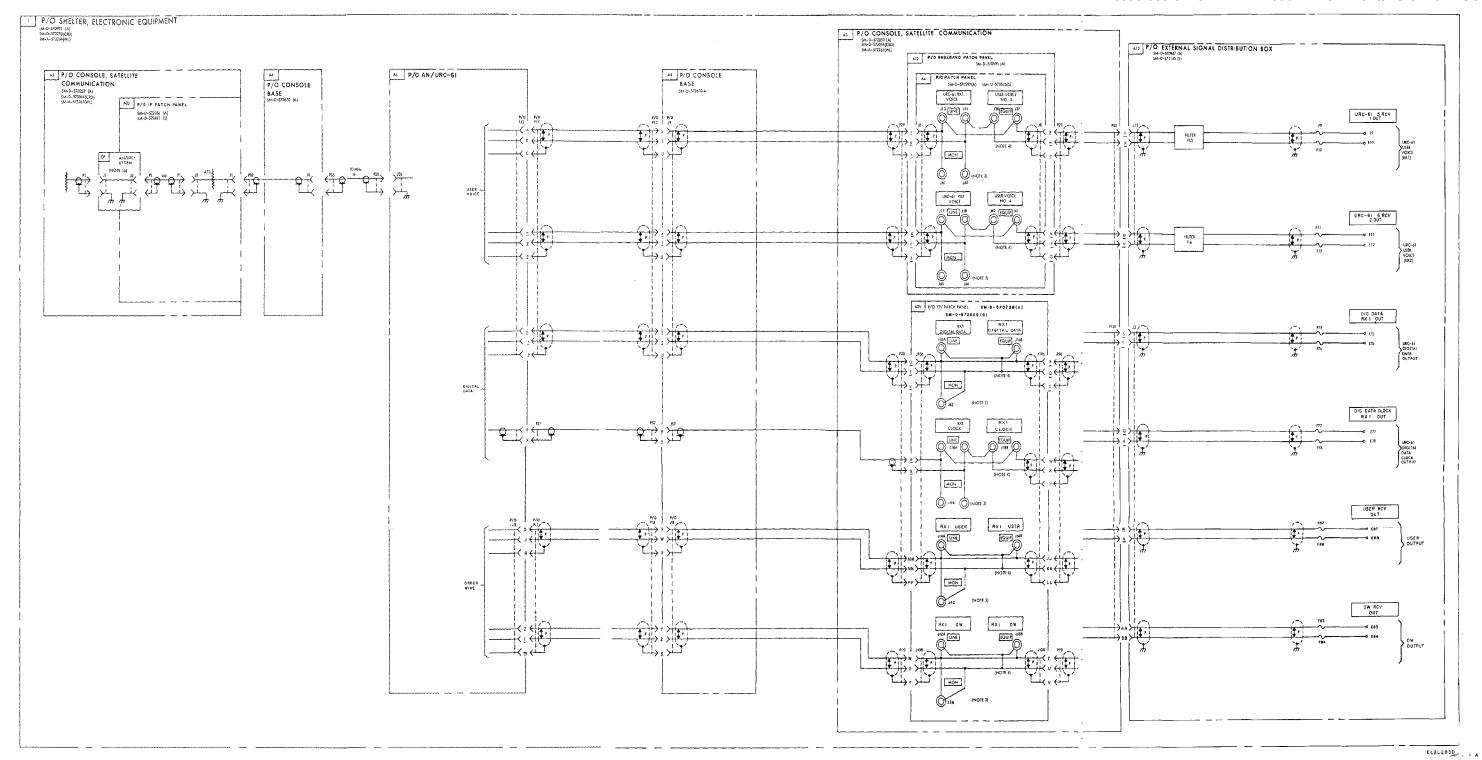

- a. All input and output signals of the AN/ TSC-54 are normalized-through patch panels to their respective circuits. The voice input signal is applied to one of three selectable filters in the normal terminal configuration. The 3995-Hz tone generator is driven by a direct current (dc) signal from a line isolation unit which provides isolation between the terminal and the external user. The 3805-Hz tone generator is driven by the AN/UGC-77 teletypewriter terminal orderwire keyboard or by an external user through a line isolation unit. The 1275-Hz tone generator is primarily for use under degraded signal conditions and is not used in normal terminal configuration.

- b. The voice signal and the two frequency shift keyed (fsk) tone signals (a above) are summed to form a composite baseband signal that is applied through preemphasis networks to modulator 1A3A14. The modulator provides a 70-MHz phase modulated (pm) signal which is routed to the if patch panel. Also available at this patch panel are the 70-MHz wideband inputs from the AN/URC-61 and the AN/TCC-79 when used with the AN/TSC-54.

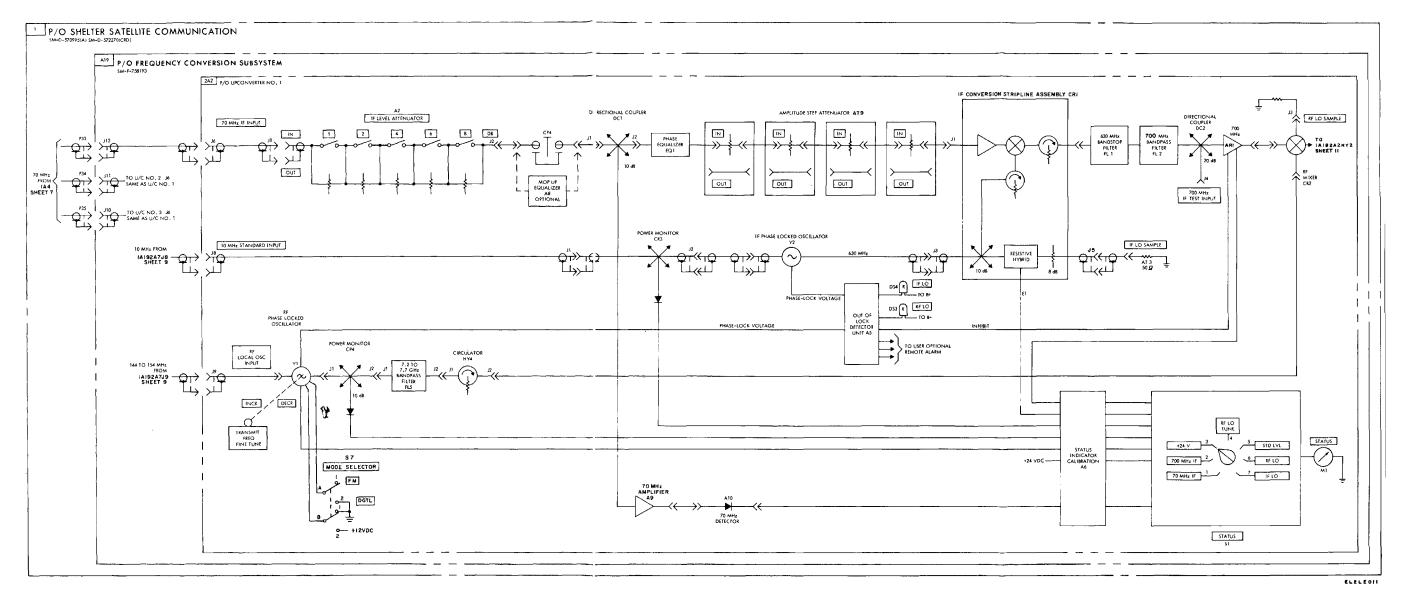

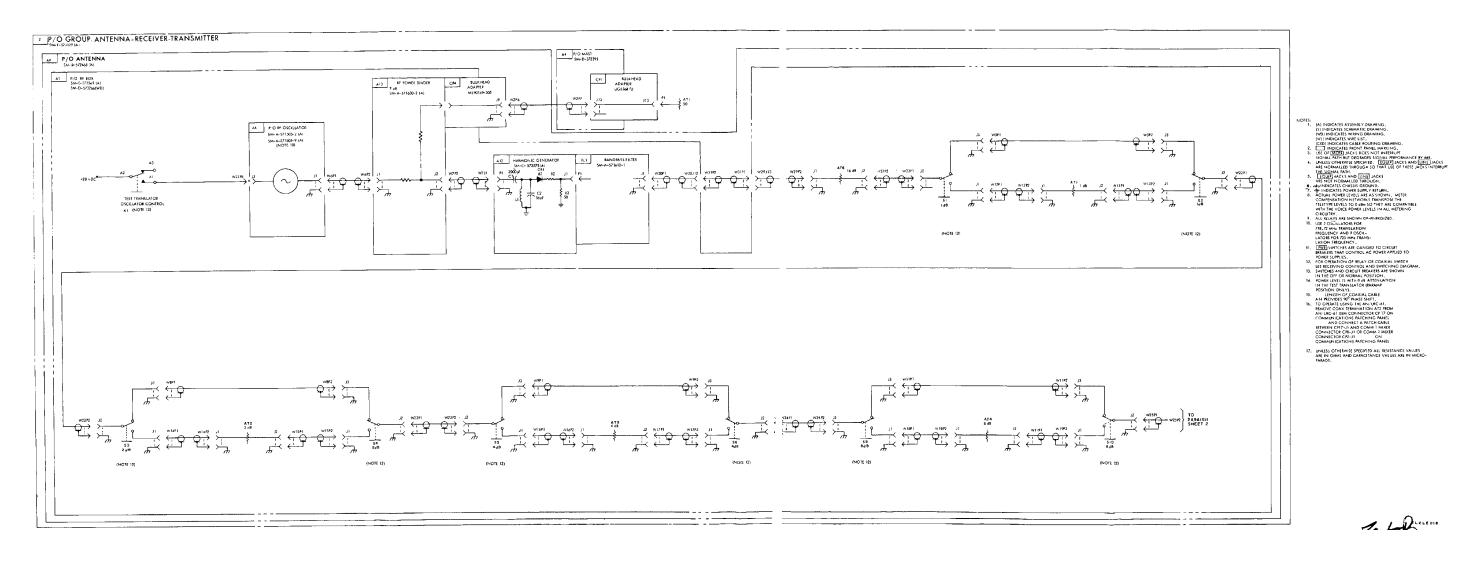

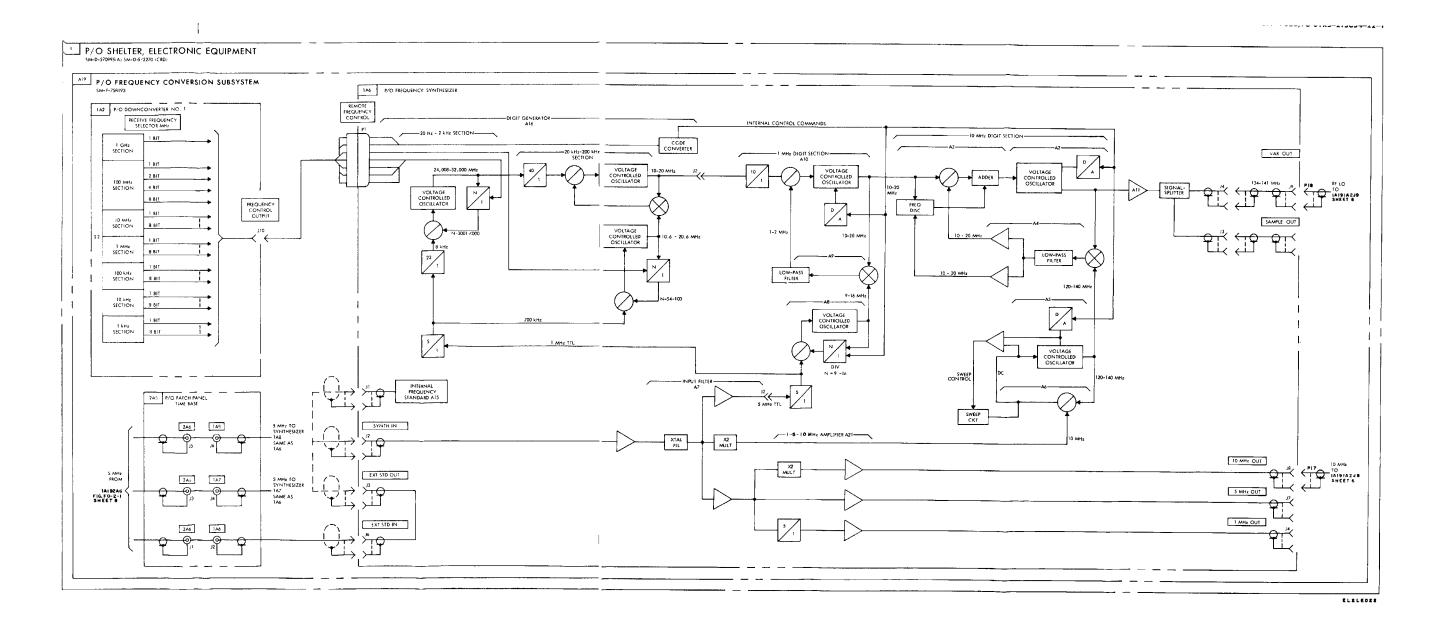

- c. The upconversion is accomplished by one of three identical upconverters. Each upconverter converts a 70-MHz signal from the if patch panel into an rf signal in the frequency range between 7.9 and 8.4

- GHz. The conversion is achieved through double-conversion process which uses first and second local oscillator frequencies of 630-MHz and 7.2 to 7.7 GHz, respectively.

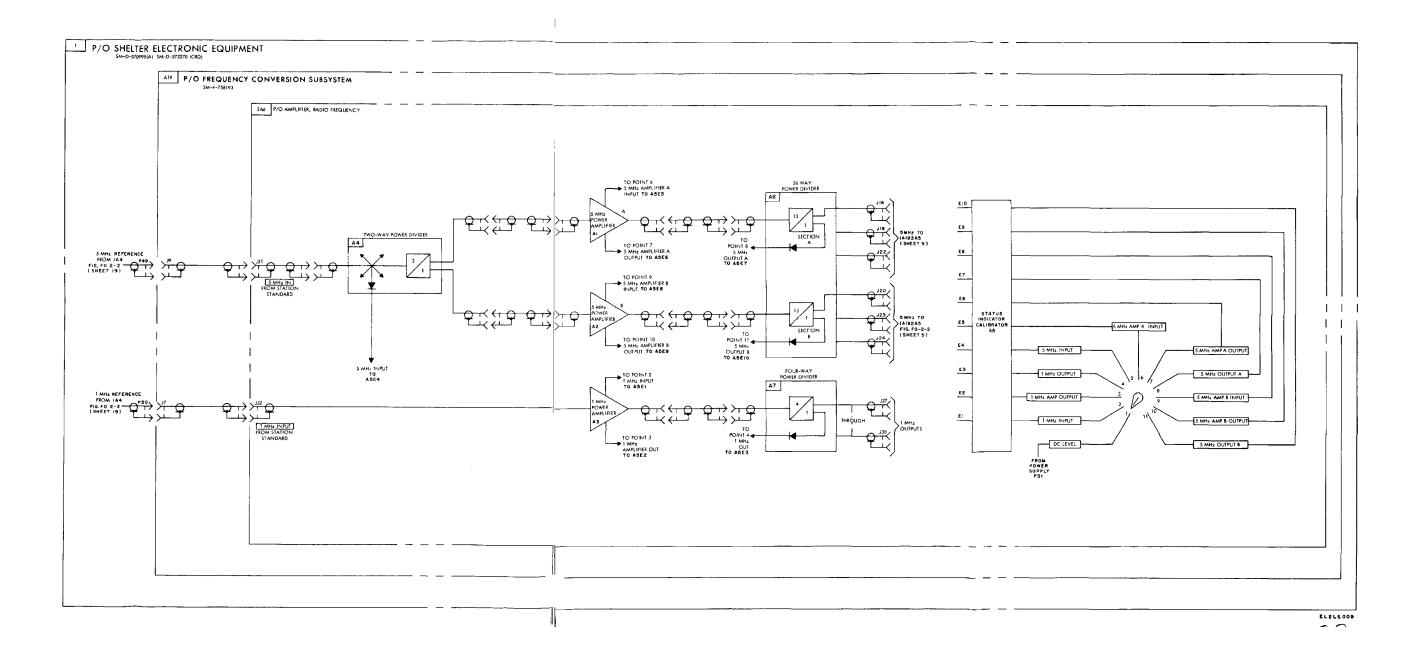

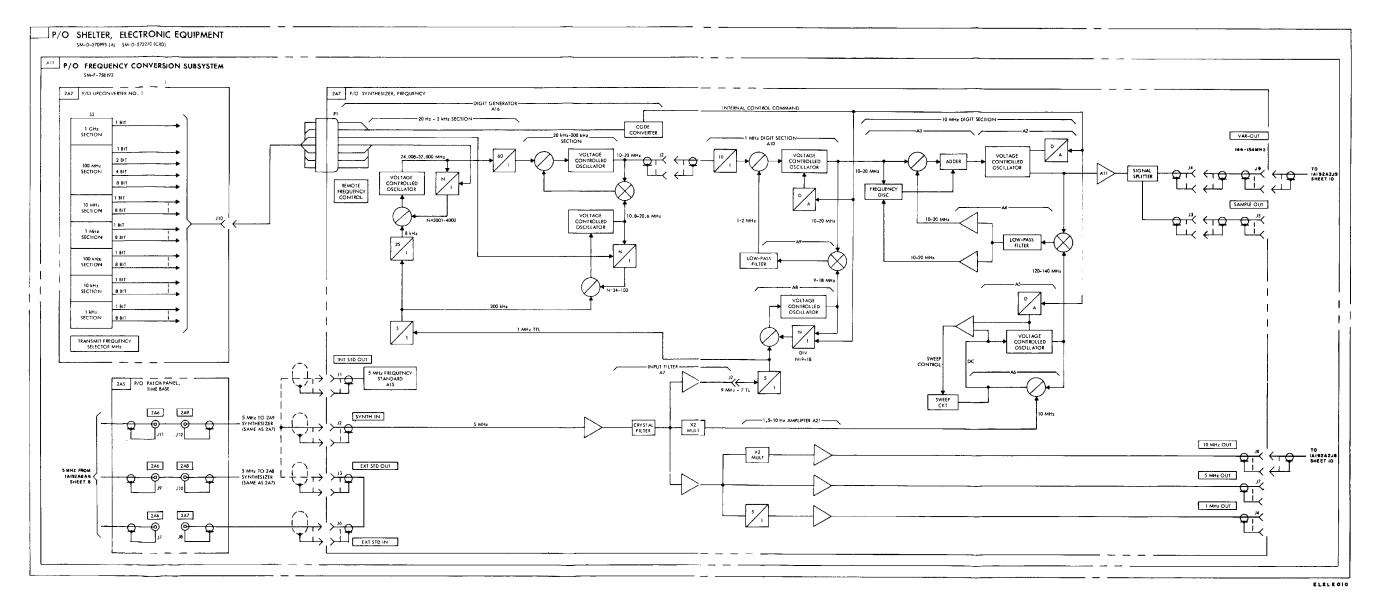

- d. The 630-MHz local oscillator signal is generated by a voltage tuned oscillator in a phase locked loop which is controlled by a 10-MHz signal from the frequency synthesizer (not shown).

he second local oscillator signal is generated y a 1. to 1.54-GHz microwave signal source which is phase locked to the 144 to 154-MHz signal from the frequency synthesizer to provide precise control and stability.

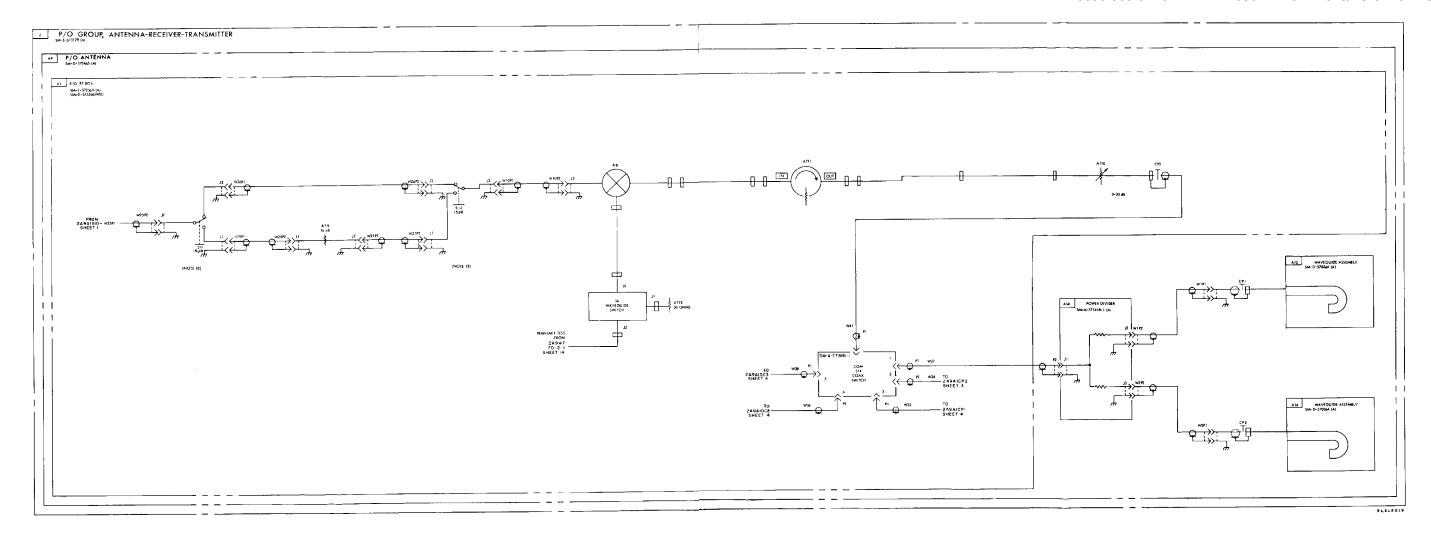

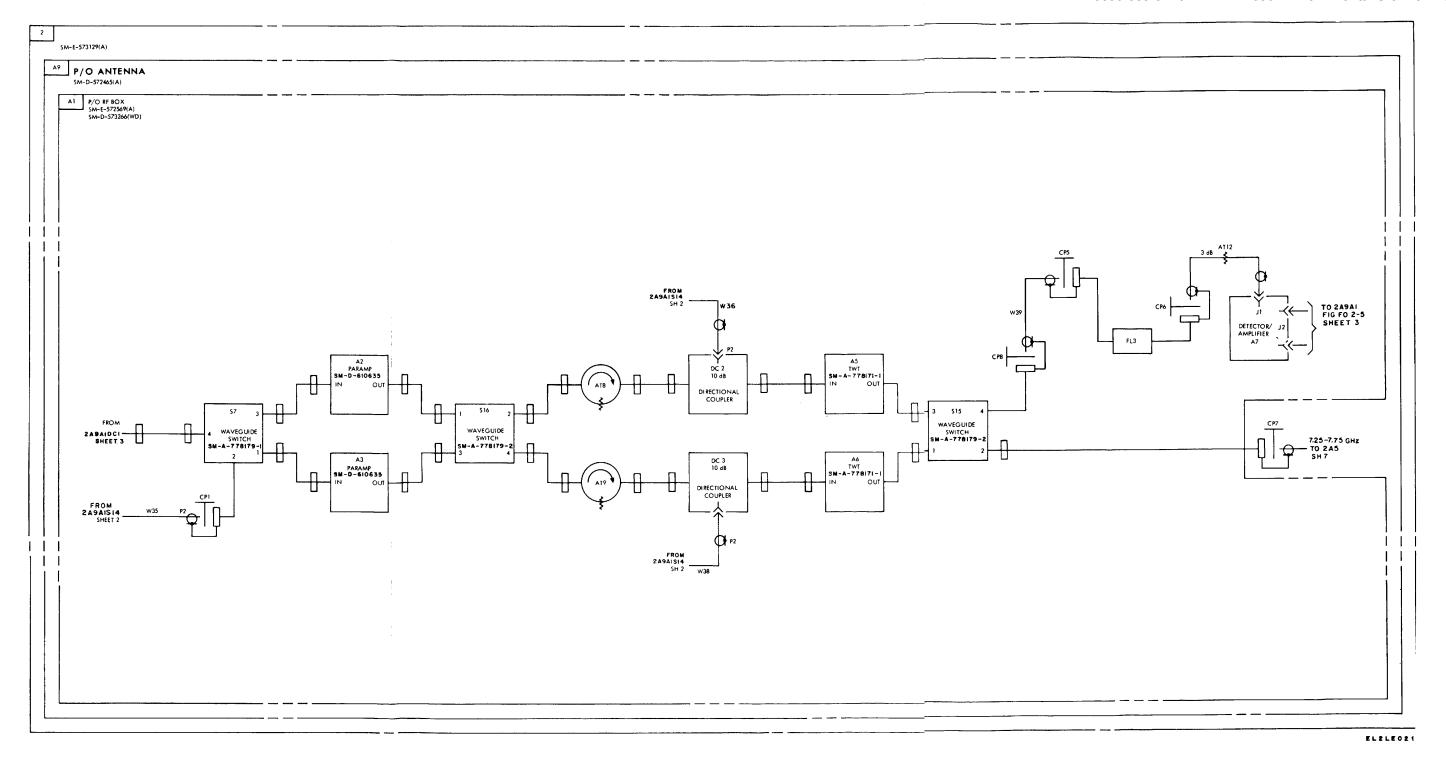

- e. The 70-MHz input from the if patch panel above) is mixed with the first local oscillator frequency to produce a 700-MHz intermediate frequency (if.). The if signal is further processed and mixed with the second local oscillator frequency to produce an rf signal in the 7.9 to 8.4 MHz range. Three upconverter outputs are combined in a waveguide power combiner (not shown). The combined upconverter outputs are applied to traveling wavetube (twt) stage. The wt is operated just in saturation and provides he necessary drive power to the klystron power amplifier. A remotely controlled attenuator allows the terminal output to be adjusted downward from a maximum of 5 kilowatts (kW) at the antenna. The output from the klystron power amplifier is applied through protective circuitry not shown) to the antenna and is subsequently radiated to the satellite.

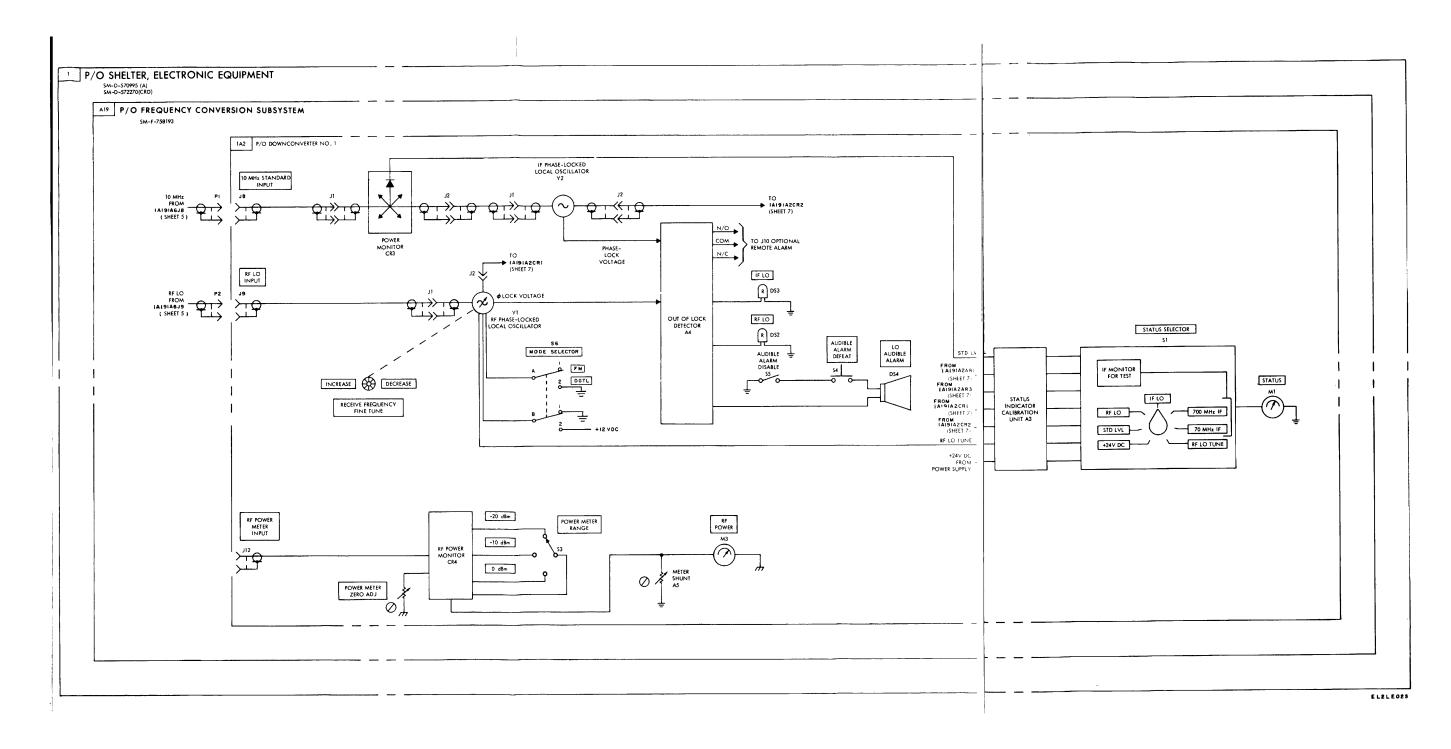

- f. The return signal from the satellite is received at the antenna and is applied to the receiver section of the The receive signal is applied through AN/TSC-54. polarizers and duplexers (not shown), which provide 20 decibels (db) of isolation from the transmitter section to permit he use of one antenna, to an uncooled, low noise, three stage, parametric amplifier (LNA). The LNA provides 30 db of gain. The output of he LNA is applied to a low noise twt amplifier 7hich provides 29 db gain to signals in the 7.25 o 7.75-GHz range. The output of the twt amplifier is applied through a waveguide power divider (not shown) to three identical downconerters. The downconverters convert the 7.25 to .75-GHz receive signal into a 70-MHz if signal. : 'his conversion is achieved through a double-conversion process which uses first and second oscillator frequencies of 6.55 to 7.05-GHz and 30-MHz, respectively.

- g. The first local oscillator signal is generated by using a 1.31 to 1.41-GHz microwave signal

Figure 1-1. Satellite Communication Terminal AN/TSC-54, simplified block diagram.

source and a 5X frequency multiplier. The signal source is phase-locked to the 131 to 141-MHz signal from the frequency synthesizer (not shown). The second local oscillator signal is generated by using a voltage tuned oscillator which operates in a ease-locked loop controlled by the 10-MHz signal from the frequency synthesizer (not shown).

h. The 7.25 to 7.75-GHz signal from the power divider (f above) is mixed with the first local oscillator frequency to produce a 700-MHz if signal. The if signal is further processed and mixed with the second local oscillator frequency provide a 70-MHz signal to the if The downconverters are capable of patch panel. simultaneous downconversion of any three satellite frequencies. The signals at the if patch panel are available for application to two communication demodulators comm. demods), one beacon demodulator (beacon emod), and the AN/URC-61. In addition, AN/ CC-79 signals are routed through the if patch panel when used with the AN/TSC-54. Each FM demodulator of the AN/TCC-79 also sends an it-of-band noise (OBN) signal to the OBN monitoring panel to provide continuous indications of circuit quality for each FM channel.

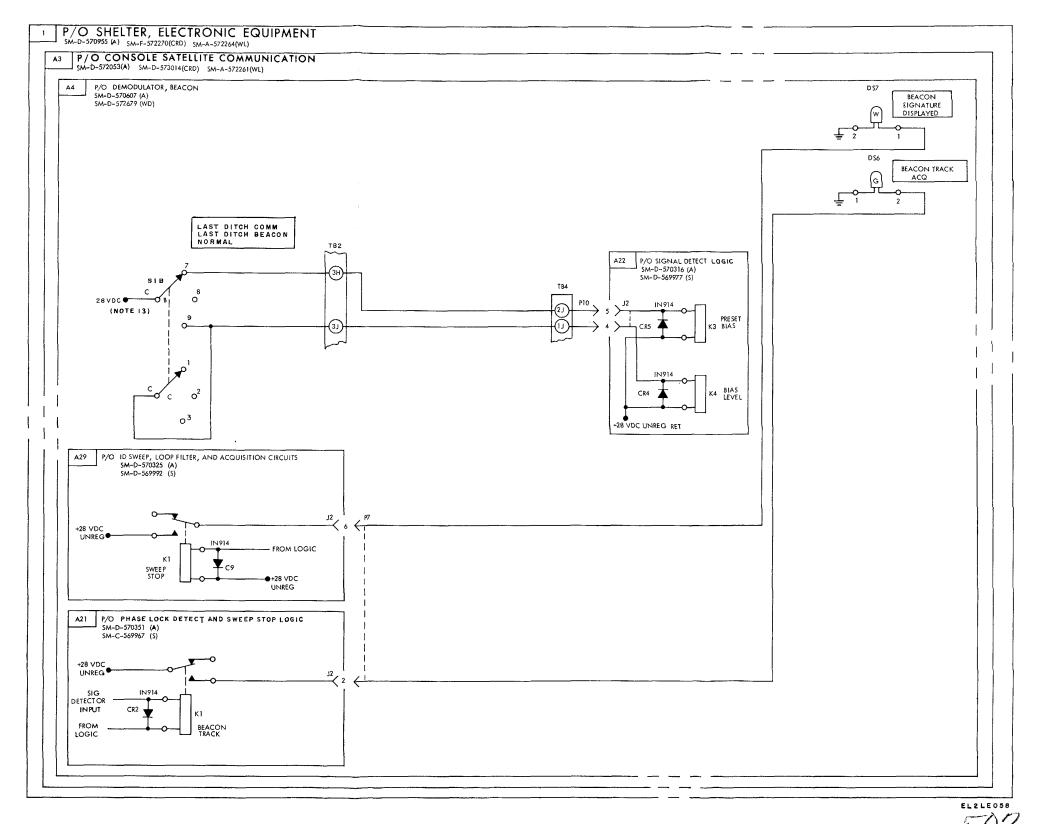

i. The beacon demod has three selectable bandwidths to provide a normal, slightly improved, ad maximum acquisition sensitivity. The beacon emod applies an autotrack (error) to the antenna control section and satellite identification signal is available on

the rear panel. The autotrack error signal enables position memory circuits within the antenna control section which allows the servo system to drive the antenna to the coordinates of he satellite. If the antenna does not lock on the satellite in four seconds the search process is repeated.

j. Each comm. demod (h above) demodulates he 70-MHz signal from the if patch panel and produces a composite signal containing voice and teletypewriter (tty) information which is applied o the deemphasis networks in the baseband section. The tty outputs from the deemphasis networks are applied through applicable fsk tone generators to the user and orderwire teletypewriters. The voice signal from the deemphasis networks is applied through one of three selectable filters to the user or orderwire handset.

#### **Tabulated Data**

Tabulated data applicable to the AN/TSC-54 is provided in TM 11-5895-389-12.

### 1-10. Reference Designations Cross References to **Figure Numbers**

To aid in the location of equipment shown on drawings, the reference designations are listed below along with the drawings on which they re shown.

| _        | ference<br>signation | Equipment                      | Figure Fold Out                                                                                                                                                                                 |

|----------|----------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1A2A1    |                      | Zero set control               | 2-3 sh 4, 2-3 sh 5, 2-8 sh 8, 2-9 sh 1.                                                                                                                                                         |

| 1A2A44   |                      | Power distribution panel       | 2-6 sh 6, 2-7 sh 1, 2-7 sh 5, 2-7 sh 9, 2-8 sh 5, 2-8 sh 8, 2-9 sh 1.                                                                                                                           |

| 1A2A5    |                      | Antenna control panel          | 2-3 sh 1, 2-3 sh 2, 2-3 sh 3, 2-3 sh 4,<br>2-3 sh 6, 2-3 sh 7, 2-3 sh 8, 2-3 sh 9,<br>2-6 sh 1, 2-6 sh 2, 2-6 sh 3, 2-6 sh 4,<br>2-6 sh 5, 2-7 sh 5, 2-7 sh 9, 2-8 sh 5,<br>2-8 sh 8, 2-9 sh 1. |

| 1A2A9    |                      | Indicator panel                | 2-8 sh 8.                                                                                                                                                                                       |

| 1A2A10   |                      | Link terminal timing central   | 2-7 sh 5, 2-7 sh 9, 2-8 sh 8.                                                                                                                                                                   |

| 1A2A21   |                      | Fan assembly                   | 2-7 sh 9.                                                                                                                                                                                       |

| 1A2A22   |                      | Frequency distribution unit    | 2-2 sh 19, 2-7 sh 5, 2-7 sh 9, 2-8 sh 8.                                                                                                                                                        |

| 1A2A24   |                      | Cesium beam frequency standard | 2-2 sh 19, 2-7 sh 5.                                                                                                                                                                            |

| 1A2A25   |                      | Cesium beam power supply       | 2-7 sh 5, 2-8 sh 8.                                                                                                                                                                             |

| 1A2A26   |                      | Test translator control        | 2-5 sh 2, 2-5 sh 3, 2-9 sh 1.                                                                                                                                                                   |

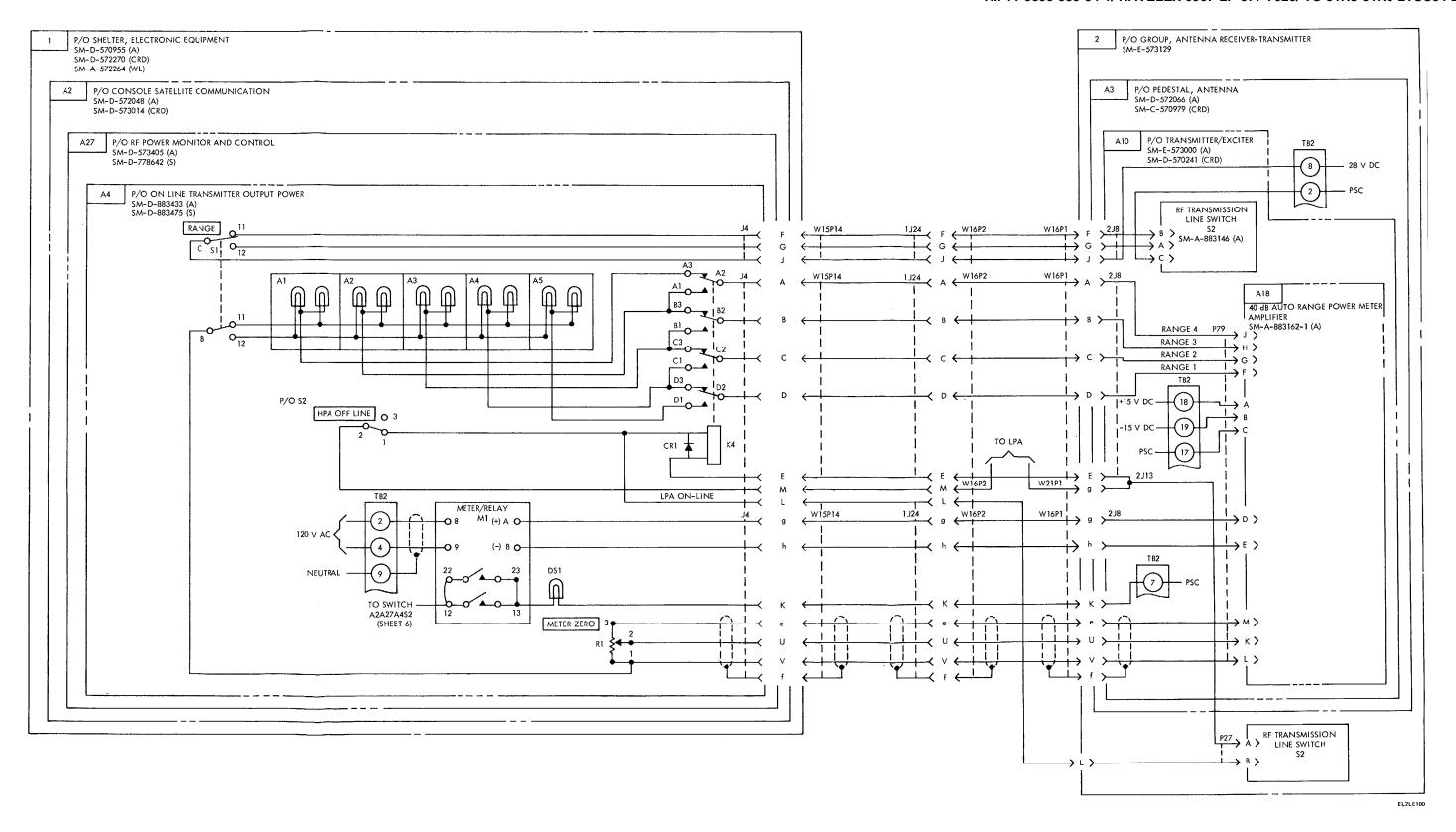

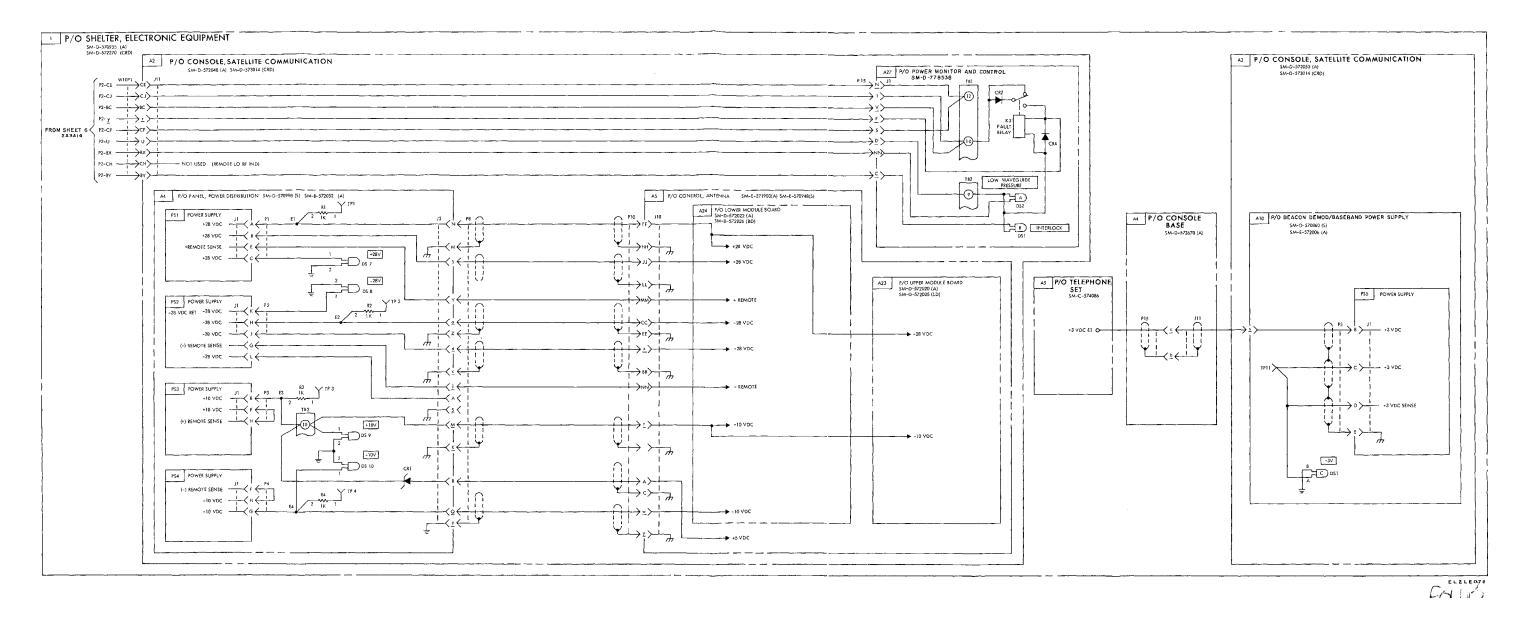

| 1A2A27   |                      | Power monitor and control      | 2-4 sh 1, 2-4 sh 2, 2-4 sh 6, 2-7 sh 5, 2-7 sh 9, 2-8 sh 5, 2-8 sh 8, 2-9 sh 1.                                                                                                                 |

| 1A2A29   |                      | Time transfer unit             | 2-2 sh 19, 2-7 sh 5, 2-7 sh 9, 2-8 sh 8.                                                                                                                                                        |

| 1A2A30/A | <del>\</del> 31      | Group delay equalizer          | 2-7 sh 5, 2-7 sh 9, 2-8 sh 8.                                                                                                                                                                   |

### TM 11-5895-389-34-1/NAVE LEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1

| Reference designation                                    | Equipment                                                                                       | Figure Fold Out                                                                                                                                                    |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1A2A33<br>1A2A34                                         | Distribution amplifier Cesium environmental                                                     | 2-2 sh 19, 2-7 sh 5, 2-7 sh 9, 2-8 sh 8.<br>2-7 sh 5, 2-7 sh 9.                                                                                                    |

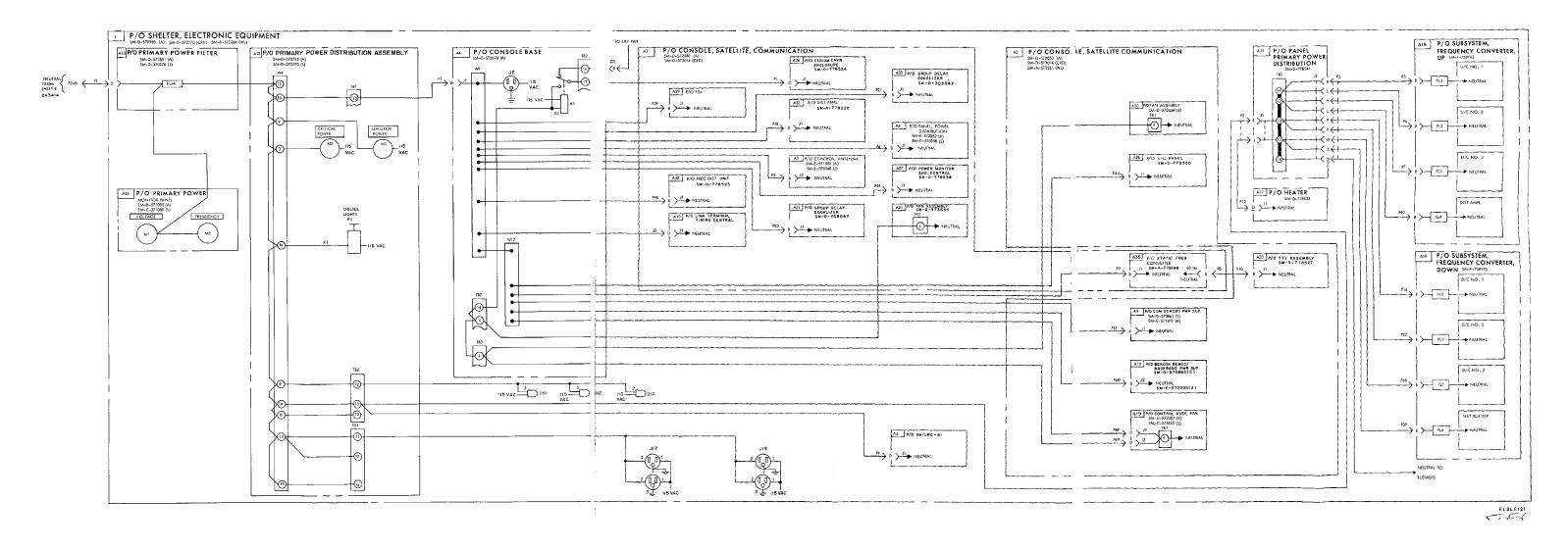

| 1A2A35                                                   | enclosure Static frequency converter                                                            | 2-7 sh 6, 2-7 sh 9.                                                                                                                                                |

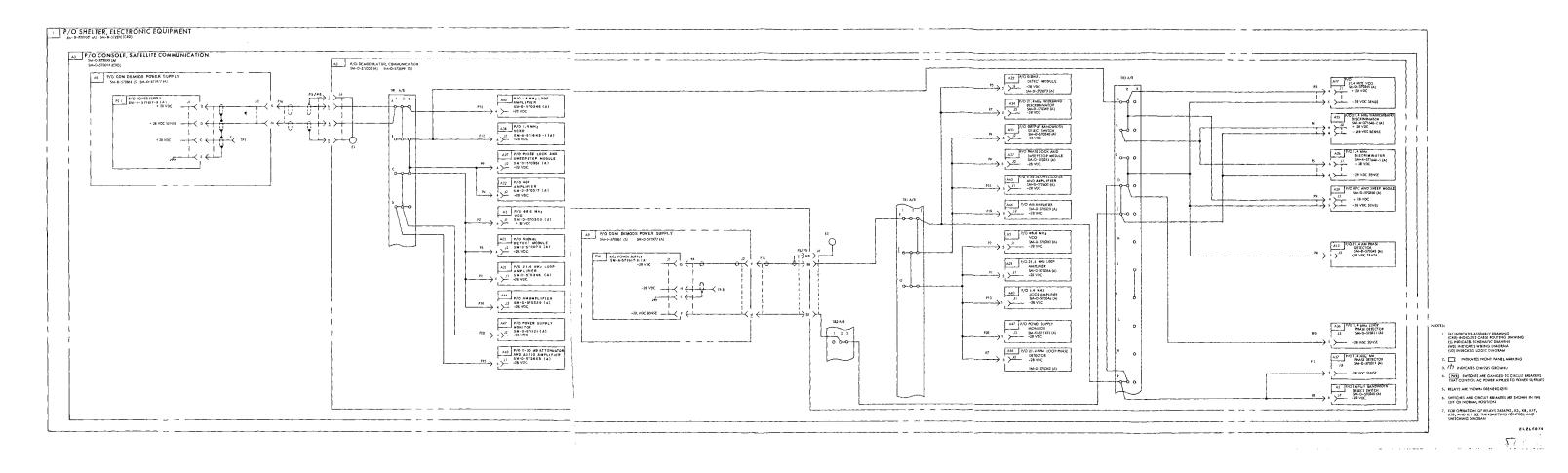

| 1A3A3                                                    | Comm demod                                                                                      | 2-1 sh 3, 2-2 sh 8, 2-2 sh 9, 2-2 sh 10,<br>2-3 sh 1, 2-5 sh 1, 2-5 sh 5, 2-8 sh 1,<br>2-8 sh 2, 2-8 sh 8, 2-9 sh 1.                                               |

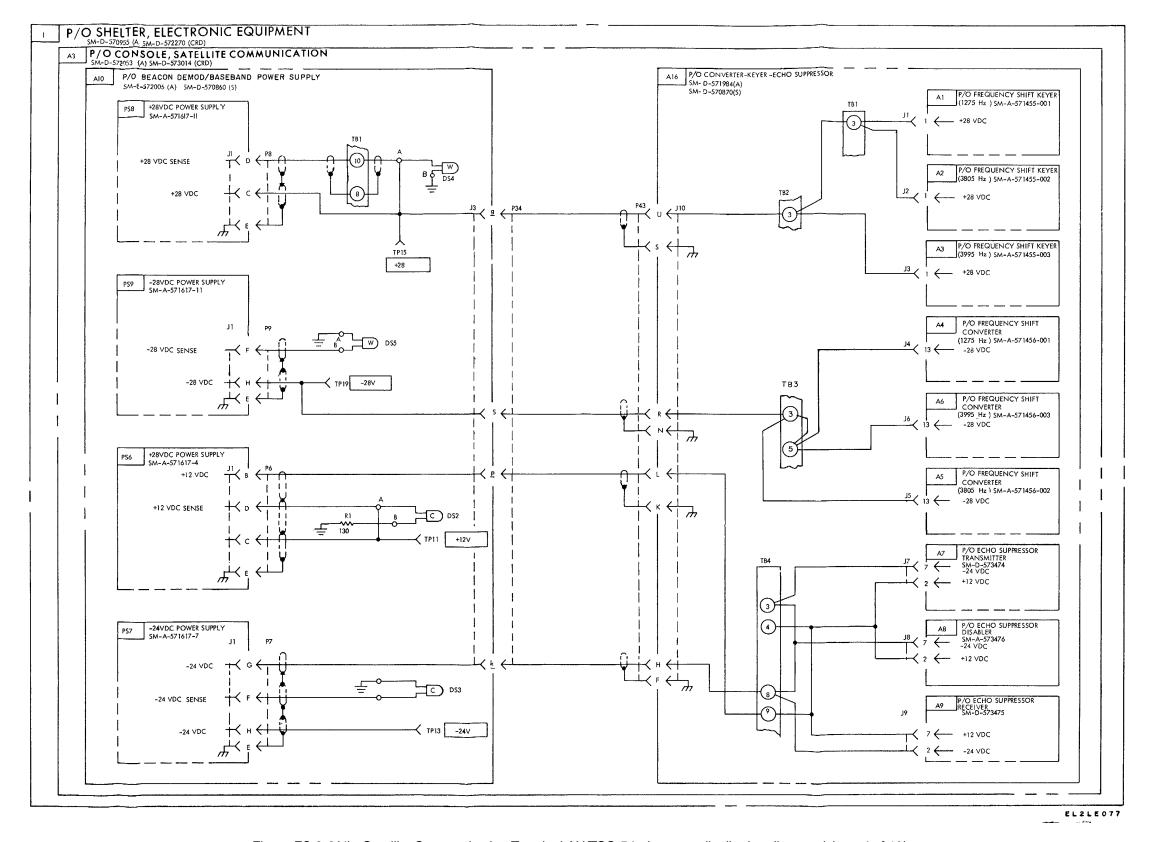

| 1A3A4                                                    | Beacon demod                                                                                    | 2-2 sh 11, 2-2 sh 12, 2-3 sh 1,<br>2-5 sh 6, 2-8 sh 8, 2-8 sh 10, 2-9 sh 1.                                                                                        |

| 1A3A5                                                    | Comm demod                                                                                      | 2-3 sh 1, 2-5 sh 5, 2-8 sh 3, 2-8 sh 8, 2-9 sh 1.                                                                                                                  |

| 1A3A9                                                    | Comm demos PS                                                                                   | 2-7 sh 6, 2-7 sh 9, 2-8 sh 1, 2-8 sh 2, 2-8 sh 3, 2-8 sh 8.                                                                                                        |

| 1A3A10                                                   | Beacon demod/<br>baseband PS                                                                    | 2-7 sh 6, 2-7 sh 9, 2-8 sh 2, 2-8 sh 3, 2-8 sh 4, 2-8 sh 8, 2-8 sh 10.                                                                                             |

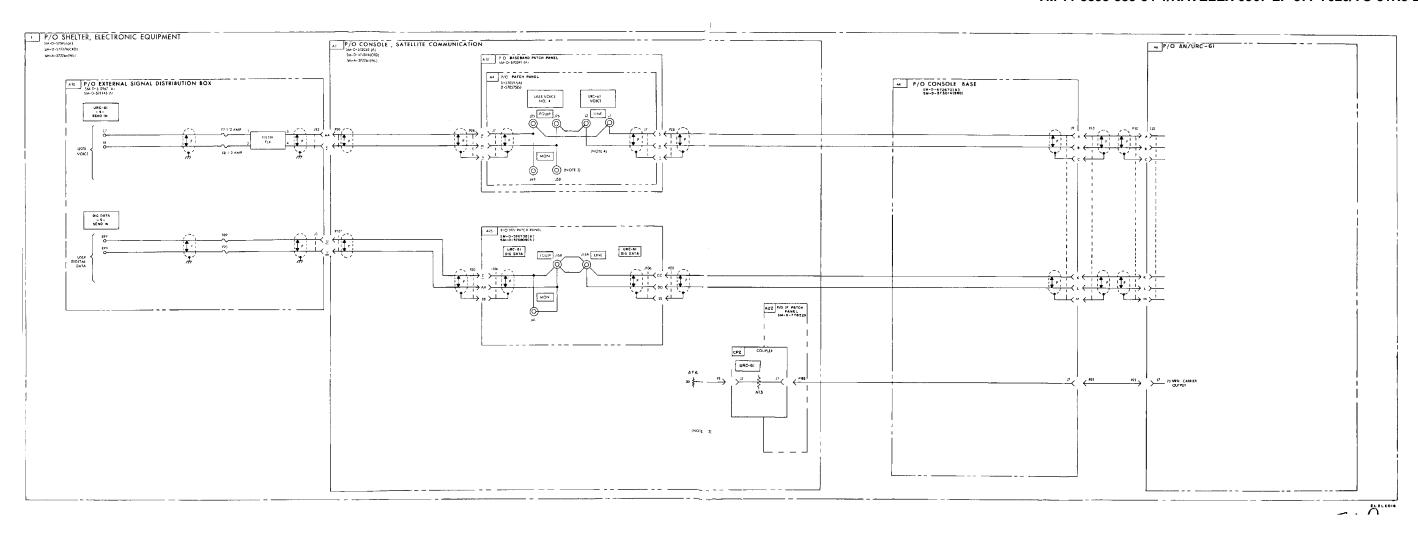

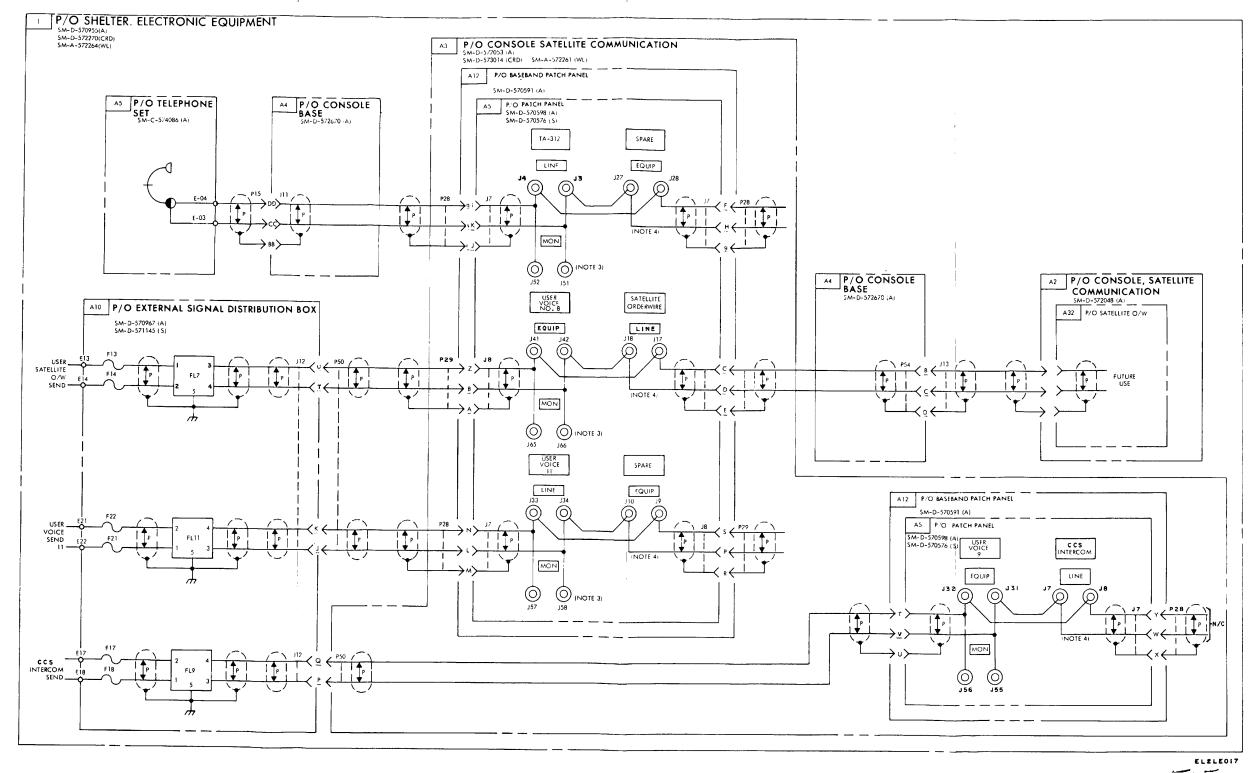

| 1A3A12                                                   | Baseband patch panel                                                                            | 2-1 sh 1, 2-1 sh 2, 2-1 sh 3, 2-1 sh 4,<br>2-1 sh 15, 2-1 sh 16, 2-2 sh 14, 2-2 sh 15,<br>2-2 sh 17, 2-2 sh 18, 2-2 sh 19, 2-8 sh 8.                               |

| 1A3A13                                                   | Baseband control panel                                                                          | 2-1 sh 1, 2-1 sh 2, 2-1 sh 3, 2-1 sh 4,<br>2-2 sh 13, 2-2 sh 15, 2-2 sh 16, 2-2 sh 17,<br>2-2 sh 18, 2-2 sh 19, 2-8 sh 2, 2-8 sh 8.                                |

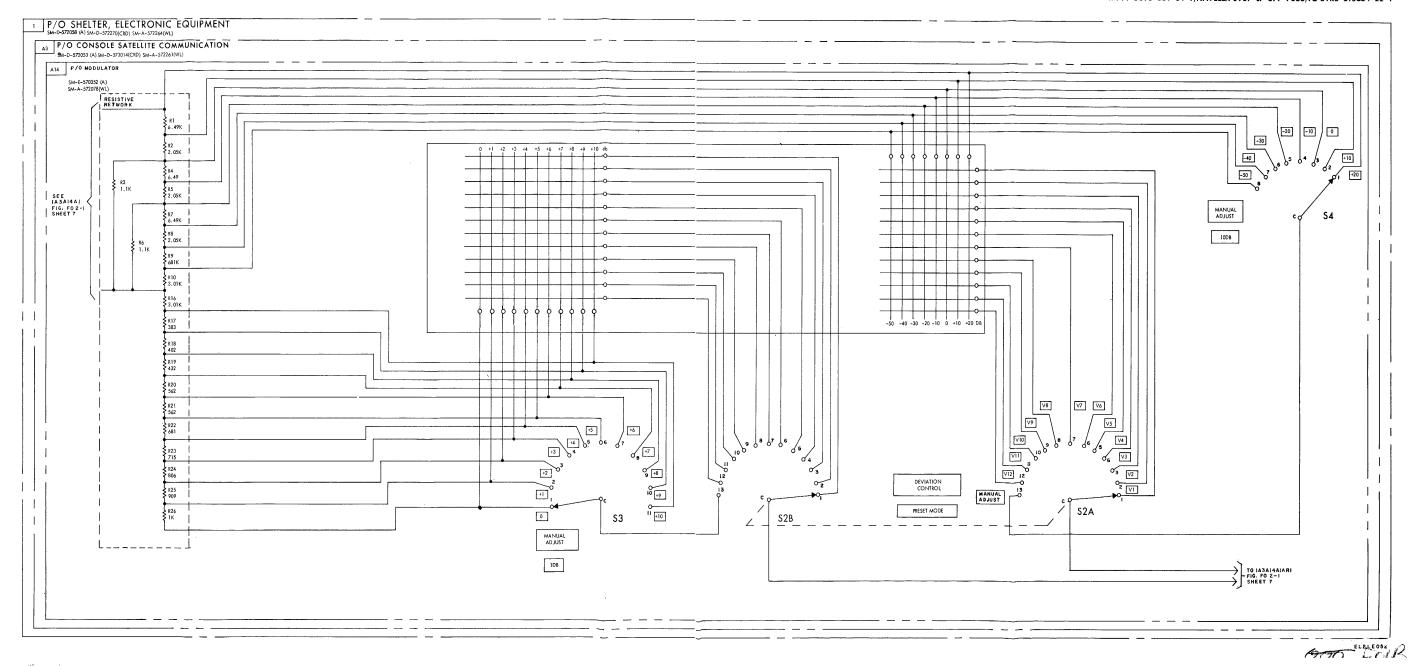

| 1A3A14                                                   | Modulator                                                                                       | 2-1 sh 7, 2-4 sh 7, 2-7 sh 6, 2-8 sh 8, 2-9 sh 1.                                                                                                                  |

| 1A3A15                                                   | Baseband amplifier                                                                              | 2-1 sh 1, 2-1 sh 5, 2-1 sh 6, 2-2 sh 14, 2-2 sh 18, 2-8 sh 3, 2-8 sh 8, 2-9 sh 1.                                                                                  |

| 1A3A16                                                   | Convertor-keyer echo suppressor                                                                 | 2-1 sh 3, 2-2 sh 16, 2-8 sh 4, 2-8 sh 8.                                                                                                                           |

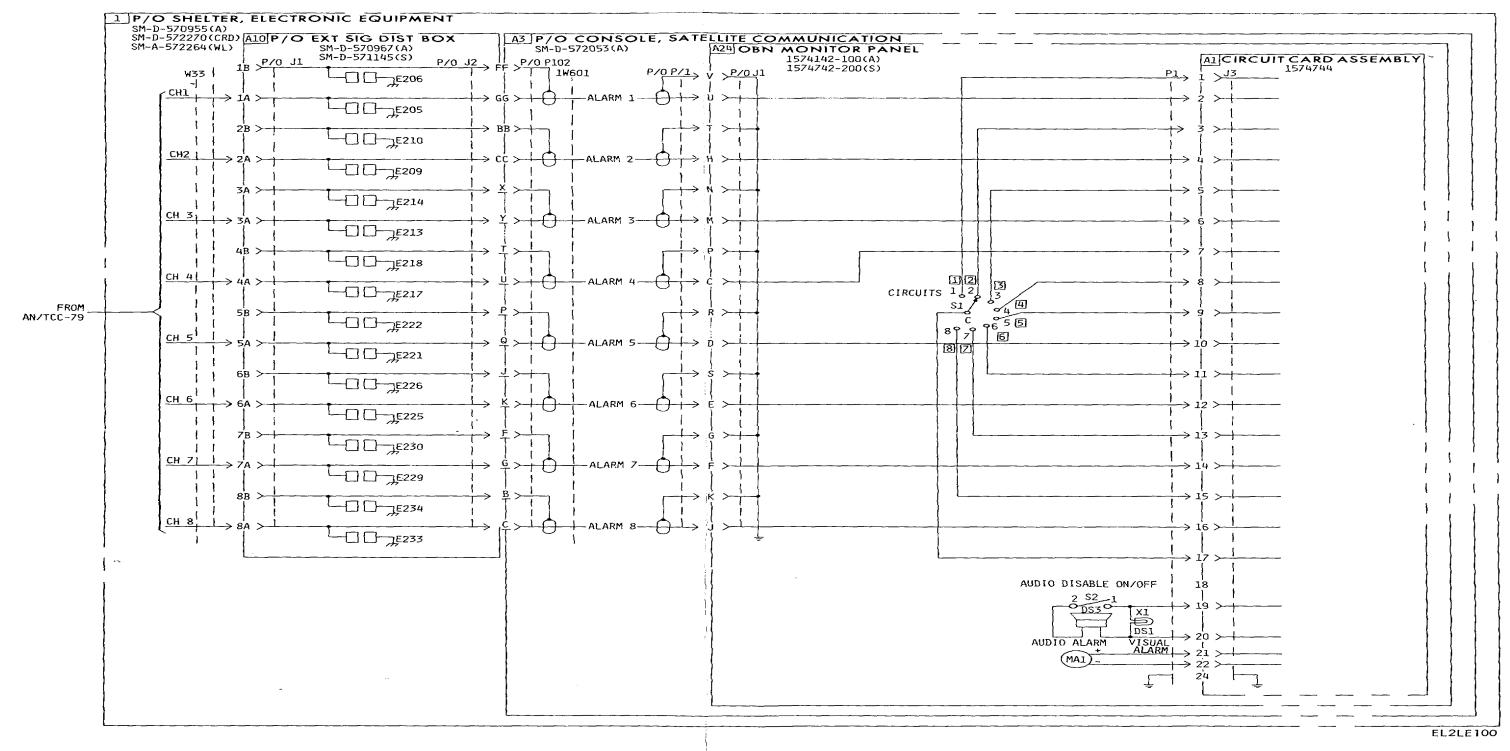

| 1A3A19<br>1A3A20<br>1A3A22<br>1A3A23<br>1A3A24<br>1A3A25 | Fan control assembly Fan assembly If patch panel Tty assembly OBN monitor panel Tty patch panel | 2-7 sh 6.<br>2-7 sh 9.<br>2-1 sh 7, 2-1 sh 15, 2-2 sh 7, 2-2 sh 13.<br>2-1 sh 2, 2-7 sh 6.<br>2-2 sh 14.1, 2-9 sh 1.<br>2-1 sh 2, 2-1 sh 13, 2-1 sh 15, 2-2 sh 13, |

| 1A3A26                                                   | LIU panel                                                                                       | 2-2 sh 17, 2-8 sh 2.<br>2-1 sh 2, 2-2 sh 17, 2-7 sh 6, 2-7 sh 9,                                                                                                   |

| 1A4                                                      | Console base                                                                                    | 2-8 sh 2.<br>2-1 sh 7, 2-1 sh 15, 2-1 sh 16, 2-2 sh 7,<br>2-2 sh 13, 2-2 sh 19, 2-5 sh 1, 2-7 sh 5,<br>2-7 sh 6, 2-7 sh 9, 2-8 sh 5, 2-8 sh 8,<br>2-9 sh 1.        |

| 1A9                                                      | Air conditioner filter asy                                                                      | 2-7 sh 4.                                                                                                                                                          |

| 1A10                                                     | External signal distri-<br>button box                                                           | 2-1 sh 2, 2-1 sh 3, 2-1 sh 4, 2-1 sh 15, 2-1 sh 16, 2-2 sh 13, 2-2 sh 15, 2-2 sh 17.                                                                               |

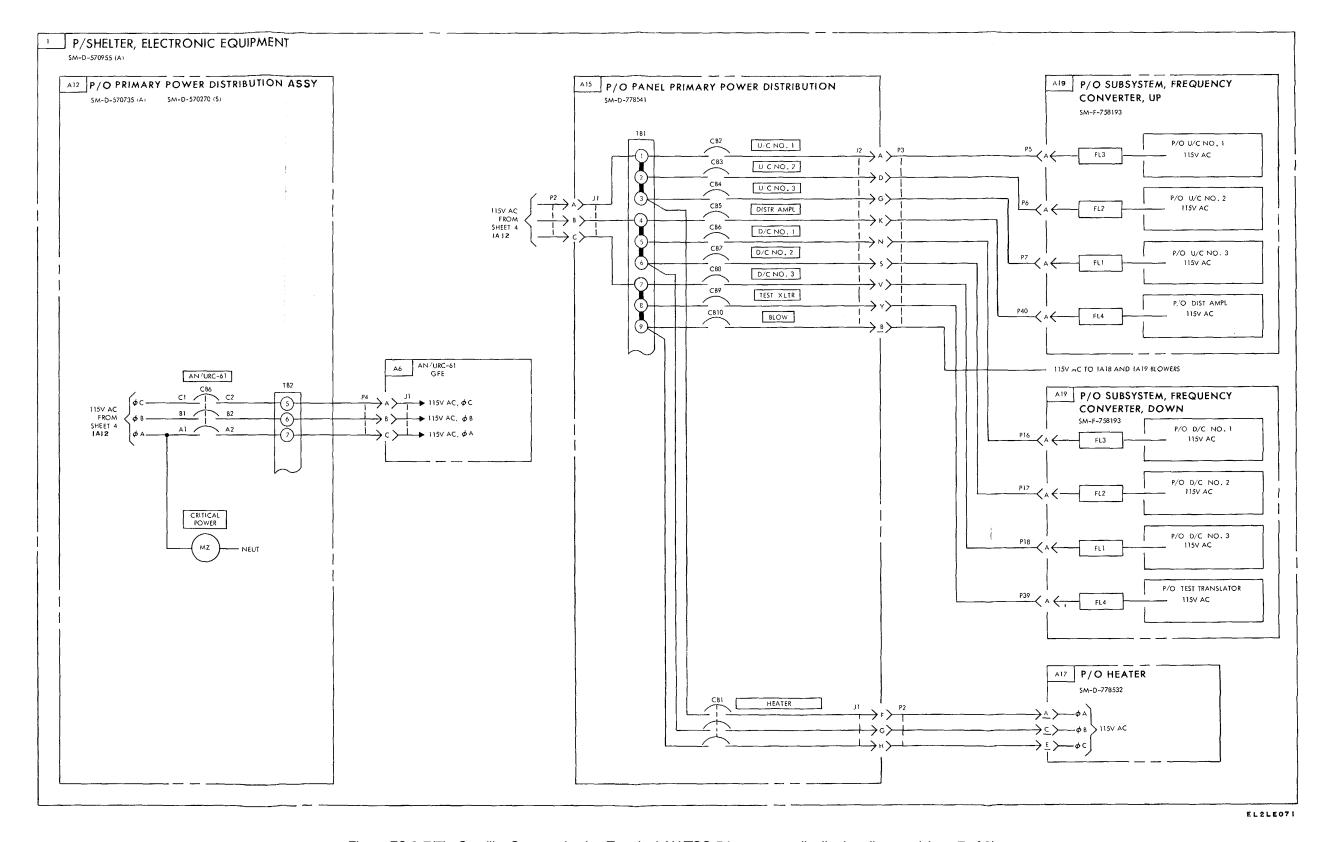

| 1A12                                                     | Primary power distrib assy                                                                      | 2-7 sh 4, 2-7 sh 7, 2-7 sh 9.                                                                                                                                      |

| 1A13<br>1A14                                             | Primary power filter External power distribution box                                            | 2-7 sh 4, 2-7 sh 9.<br>2-8 sh 8.                                                                                                                                   |

| 1A15                                                     | Primary power distribution panel                                                                | 2-7 sh 7, 2-7 sh 9, 2-8 sh 8.                                                                                                                                      |

| 1A17                                                     | Shelter heater                                                                                  | 2-7 sh 7.                                                                                                                                                          |

### TM 11-5895-389-34-1/NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1

| Reference designation                           | Equipment                                                | Figure Fold Out                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

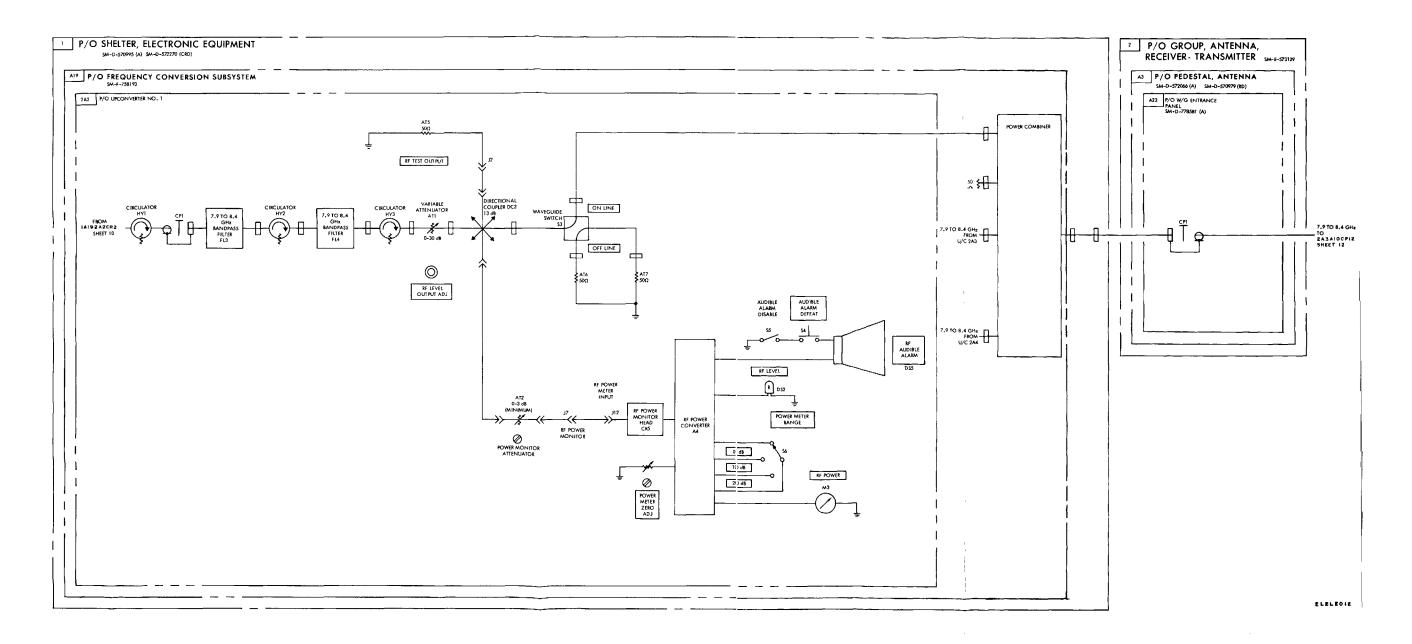

| 1A19                                            | Freq conversion S/S                                      | 2-1 sh 8, 2-1 sh 9, 2-1 sh 10, 2-1 sh 11,<br>2-2 sh 5, 2-2 sh 6, 2-2 sh 7, 2-5 sh 4,<br>2-7 sh 7, 2-7 sh 9, 2-8 sh 8.                                                                                                                                                                                               |

| 2A2                                             | Power supply                                             | 2-4 sh 3, 2-4 sh 4,<br>2-8 sh 7, 2-8 sh 9.                                                                                                                                                                                                                                                                          |

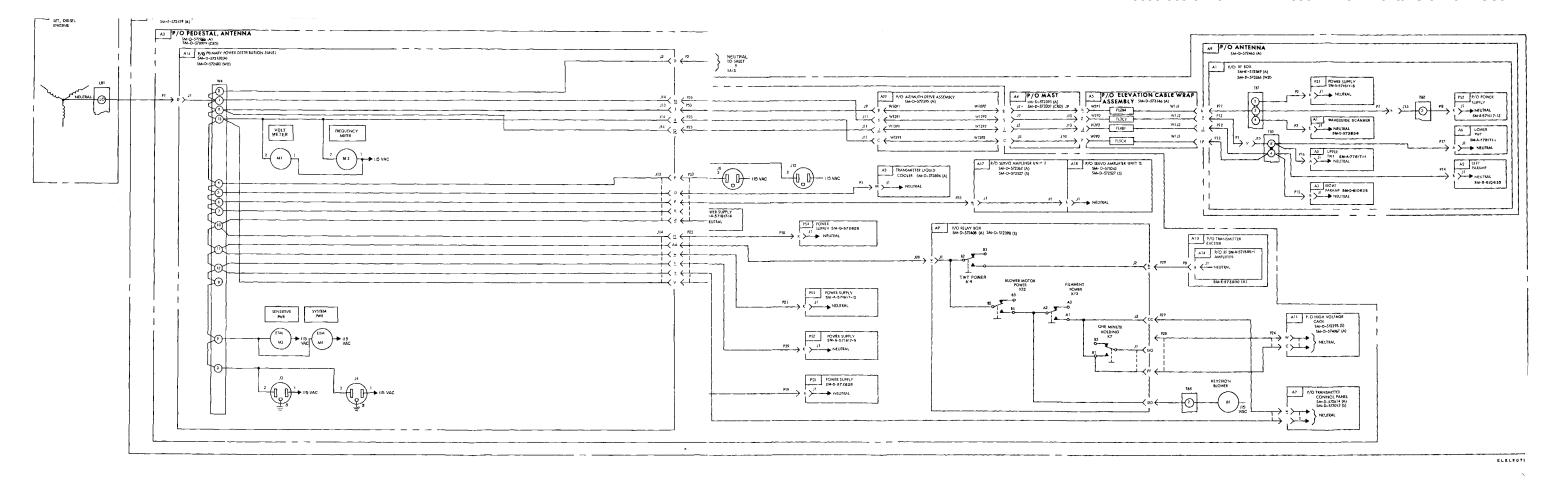

| 2A3A3                                           | Transmitter liquid cooler                                | 2-4 sh 3, 2-7 sh 3, 2-7 sh 8, 2-9 sh 2, 2-10.                                                                                                                                                                                                                                                                       |

| 2A3A7                                           | Transmitter control panel                                | 2-1 sh 14, 2-4 sh 1, 2-4 sh 2, 2-4 sh 4,<br>2-1 sh 5, 2-4 sh 6, 2-7 sh 3, 2-7 sh 8,<br>2-8 sh 6, 2-8 sh 9, 2-9 sh 2.                                                                                                                                                                                                |

| 2A3A9                                           | Relay box assembly                                       | 2-4 sh 1, 2-4 sh 2, 2-4 sh 3, 2-4 sh 4,<br>2-4 sh 6, 2-7 sh 1, 2-7 sh 3, 2-7 sh 8,<br>2-8 sh 6, 2-8 sh 9, 2-9 sh 2.                                                                                                                                                                                                 |

| 2A3A10                                          | Transmitter/exciter                                      | 2-1 sh 12, 2-1 sh 13, 2-1 sh 14, 2-4 sh 1,<br>2-4 sh 2, 2-4 sh 3, 2-4 sh 4, 2-4 sh 5,<br>2-4 sh 6, 2-7 sh 1, 2-7 sh 3, 2-7 sh 8,<br>2-8 sh 6, 2-8 sh 7, 2-8 sh 9, 2-9 sh 2,<br>2-10.                                                                                                                                |

| 2A3A11                                          | High voltage cage                                        | 2-4 sh 2, 2-4 sh 3, 2-4 sh 4, 2-7 sh 1,<br>2-7 sh 3, 2-7 sh 8, 2-8 sh 6, 2-8 sh 7,<br>2-8 sh 9, 2-9 sh 2.                                                                                                                                                                                                           |

| 2A3A14                                          | Primary power distribution panel                         | 2-1 sh 14, 2-3 sh 4, 2-3 sh 5, 2-3 sh 9,<br>2-4 sh 1, 2-4 sh 2, 2-4 sh 3, 2-4 sh 3, 2-4 sh 6,<br>2-6 sh 1, 2-6 sh 6, 2-7 sh 1, 2-7 sh 2,<br>2-7 sh 3, 2-7 sh 4, 2-7 sh 8, 2-8 sh 6,                                                                                                                                 |

| 2A3A17                                          | Servo amplifier                                          | 2-8 sh 9, 2-9 sh 2, 2-12.<br>2-3 sh 9, 2-6 sh 6, 2-7 sh 3, 2-7 sh 8,<br>2-8 sh 9, 2-9 sh 2.                                                                                                                                                                                                                         |

| 2A3A18<br>2A3A20                                | Servo amplifier<br>High voltage plate                    | 2-6 sh 6, 2-7 sh 3, 2-7 sh 8.<br>2-4 sh 2, 2-4 sh 4, 2-7 sh 1, 2-7 sh 3,<br>2-8 sh 9.                                                                                                                                                                                                                               |

| 2A3A21<br>2A3A22                                | Magnet power supply Azimuth drive assembly               | 2-8 sh 6, 2-8 sh 7.<br>2-1 sh 14, 2-3 sh 4, 2-3 sh 5, 2-3 sh 9,<br>2-4 sh 1, 2-5 sh 2, 2-5 sh 3, 2-6 sh 1,<br>2-6 sh 6, 2-7 sh 2, 2-7 sh 3, 2-7 sh 8,<br>2-8 sh 7, 2-9 sh 2, 2-12.                                                                                                                                  |

| 2A3A23<br>2A3A24                                | Waveguide entrance<br>Intercom/Air monitor<br>panel      | 2-1 sh 11, 2-2 sh 7.<br>2-8 sh 7, 2-12.                                                                                                                                                                                                                                                                             |

| 2A3PS1<br>2A3PS2<br>2A3PS3<br>2A3PS4/PS5<br>2A4 | Power supply Power supply Power supply Power supply Mast | 2-7 sh 2, 2-7 sh 8, 2-8 sh 6, 2-8 sh 9.<br>2-7 sh 2, 2-7 sh 8, 2-8 sh 6, 2-8 sh 9.<br>2-7 sh 2, 2-7 sh 8, 2-8 sh 7, 2-8 sh 9.<br>2-7 sh 1, 2-7 sh 8, 2-8 sh 7, 2-8 sh 9.<br>2-1 sh 14, 2-2 sh 1, 2-2 sh 7, 2-3 sh 3,<br>2-3 sh 5, 2-4 sh 1, 2-5 sh 2, 2-5 sh 3,<br>2-6 sh 6, 2-7 sh 8, 2-8 sh 7, 2-8 sh 9,<br>2-12. |

| 2A4A3                                           | Servo amplifier                                          | 2-3 sh 9, 2-6 sh 6, 2-7 sh 2, 2-7 sh 3, 2-8 sh 9.                                                                                                                                                                                                                                                                   |

| 2A4A4<br>2A4A6                                  | Servo amplifier<br>Elevation data box<br>synchro         | 2-3 sh 9, 2-6 sh 6, 2-7 sh 2.<br>2-6 sh 1, 2-9 sh 3.                                                                                                                                                                                                                                                                |

| 2A4A9                                           | Antenna                                                  | 2-1 sh 14.                                                                                                                                                                                                                                                                                                          |

## TM 11-5895-389-34-1/NAVELEX 0967-LP-377-7020/TO 31R5-2TSC54-22-1

| Reference designation | Equipment            | Figure Fold Out                         |

|-----------------------|----------------------|-----------------------------------------|

| 2A4B1                 | Drive motor          | 2-3 sh 9.                               |

| 2A5                   | Elevation cable wrap | 2-2 sh 7, 2-3 sh 3, 2-5 sh 2, 2-5 sh 3, |

|                       | ·                    | 2-6 sh 1, 2-6 sh 6, 2-7 sh 2, 2-7 sh 8, |

|                       |                      | 2-8 sh 7, 2-8 sh 9, 2-12.               |

| 2A9A1                 | Rf box               | 2-1 sh 1, 2-1 sh 2, 2-1 sh 3, 2-1 sh 4, |

|                       |                      | 2-3 sh 3, 2-5 sh 2, 2-5 sh 3, 2-6 sh 6, |

|                       |                      | 2-7 sh 2, 2-7 sh 8, 2-8 sh 7, 2-8 sh 9, |

|                       |                      | 2-9 sh 3, 2-12.                         |

**Change 2 1-7**

## CHAPTER 2 FUNCTIONING OF EQUIPMENT

#### Section I. INTRODUCTION

#### 2-1. General

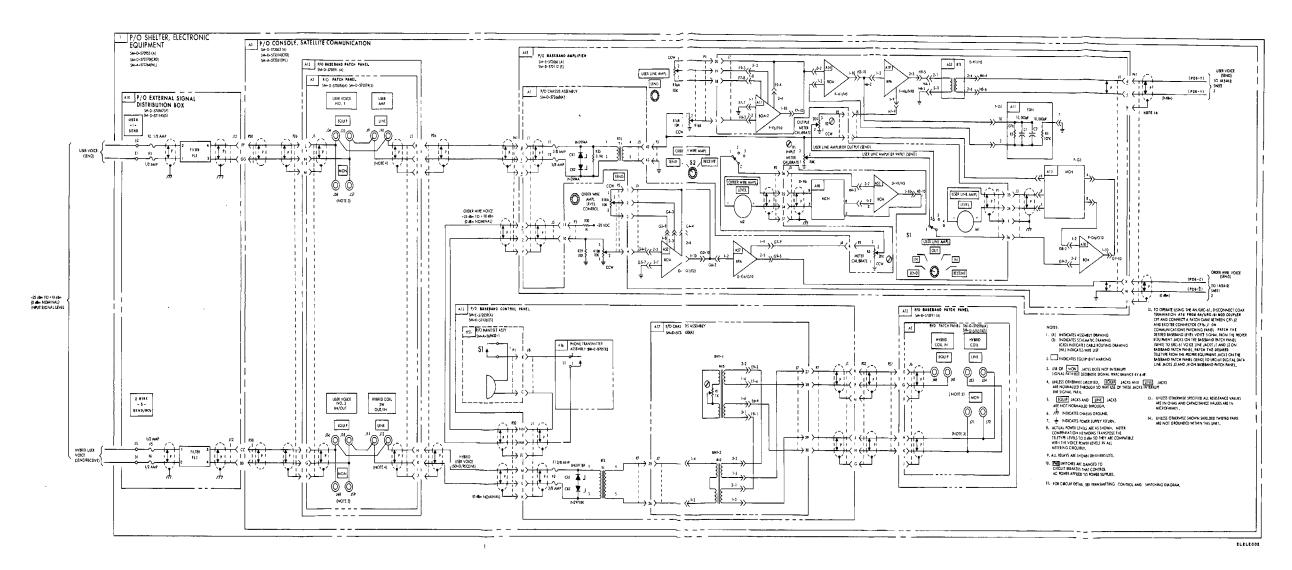

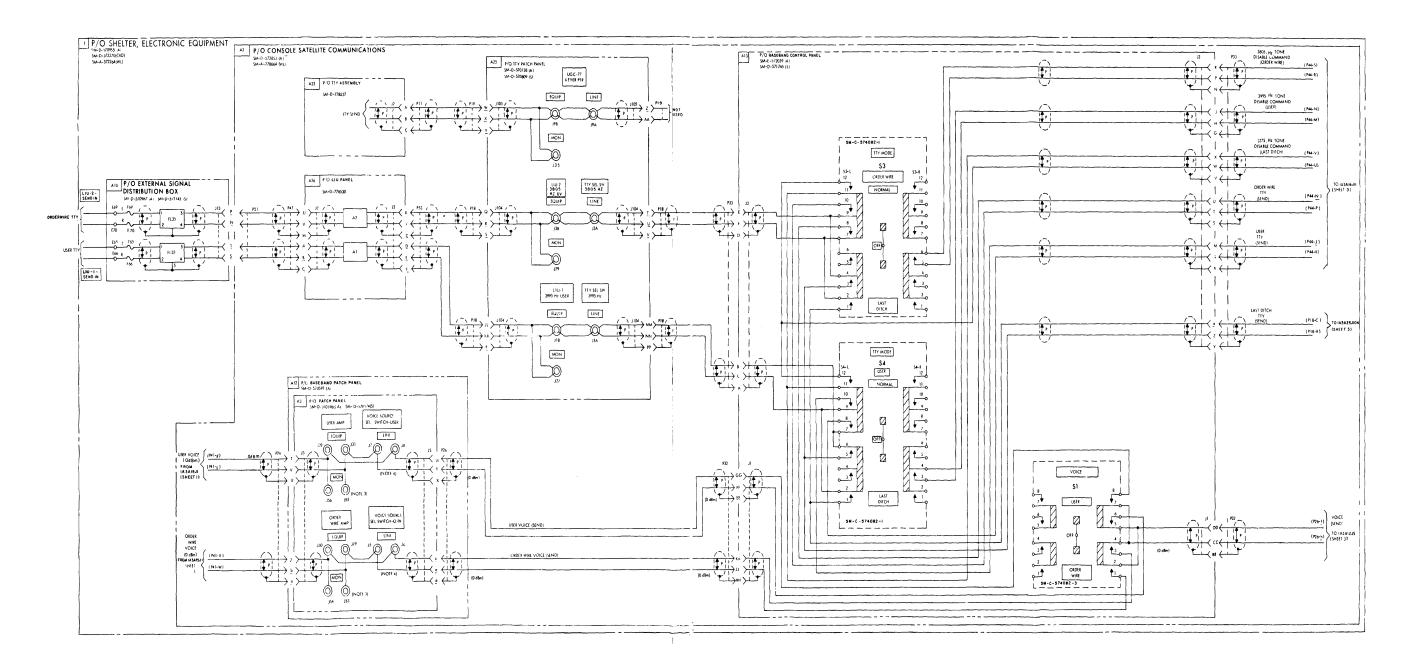

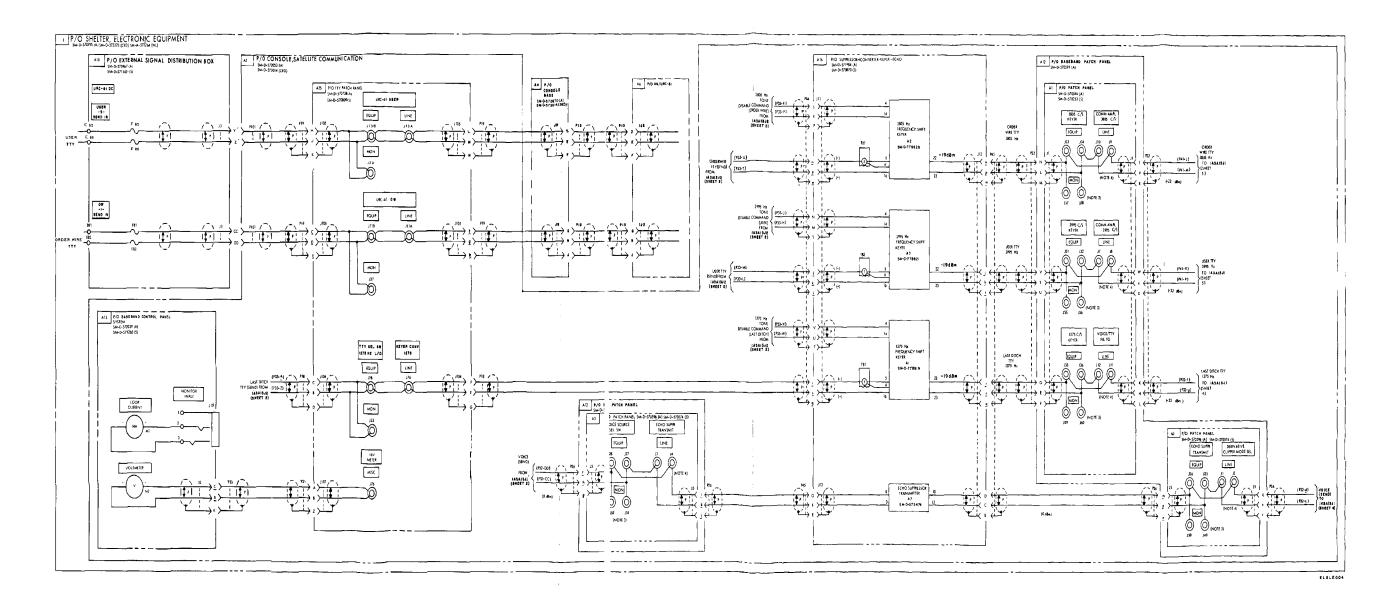

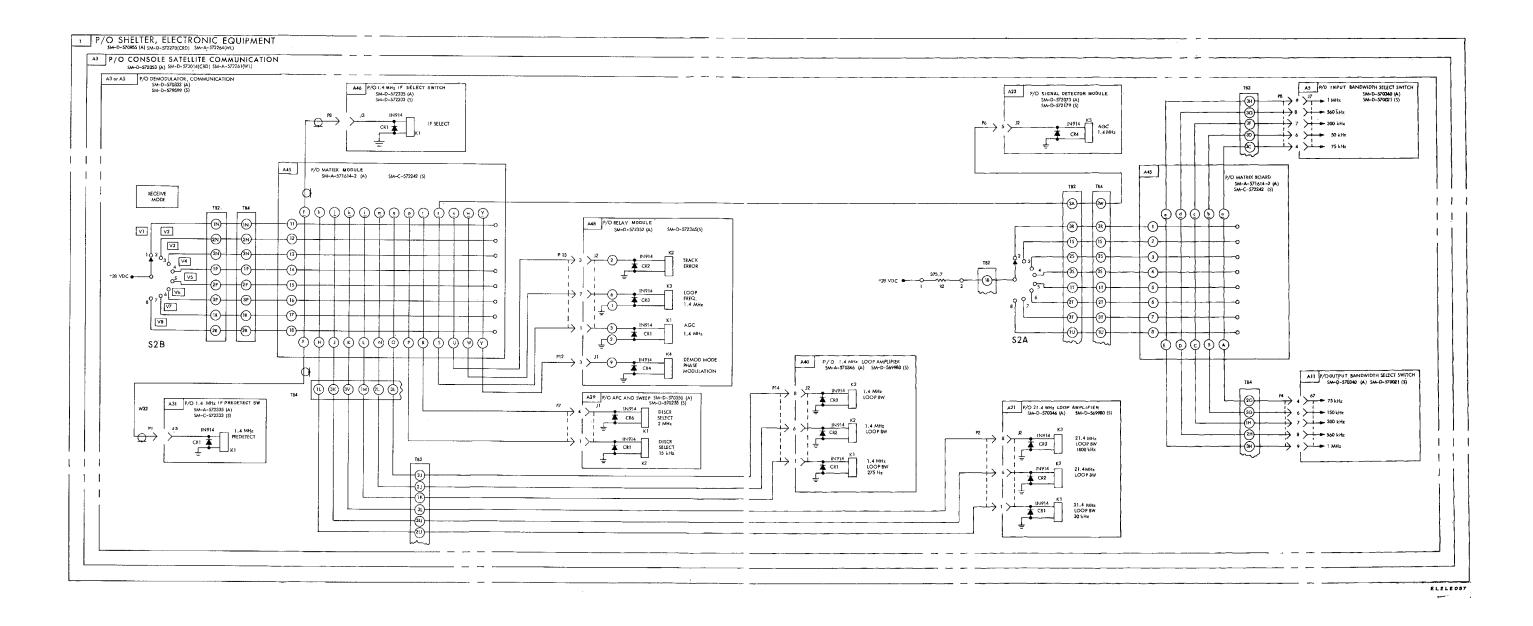

- a. This chapter contains a functional diagram analysis of each major component of Satellite Communication Terminal AN/TSC-54. The functional diagrams illustrate signal, control, and power distribution paths within the AN/ TSC-54 from their points of origin to their points of termination (closed loop). The individual circuit paths are traced through units, modular assemblies, subassemblies, and circuit stages regardless of their physical location.

- b. Circuit components (piece parts) are not shown on the functional diagrams except where they are necessary to clarify the action of a circuit upon a particular signal. Each function and operational characteristic of the individual components of the AN/TSC-54 is described in detail to provide a complete understanding of the operation of the equipment.

- c. Many of the circuit stages in the AN/TSC54 are identical, differing only in reference designations of components parts. For purposes of this manual, only the transmitting, receiving, antenna positioning and control functions of the equipment are described. Detailed theory of the individual circuit stages within the block symbols shown on the functional diagrams, are covered in chapter 3.

- d. Cross-reference to portions of multipart functional diagrams are made in the text to identify the point on the illustration at which the component and/or connections are made.

#### 2-2. Types of Functional Diagrams

Three types of functional diagrams are used to describe the operational characteristics of the AN/TSC-54. The functional diagrams are contained in this manual.

a. Signal Flow Diagrams. Signal flow diagrams illustrate the circuit paths of transmitted, received, antenna positioning, and telephone signals throughout the AN/TSC-54. The individual circuit paths are essentially determined by the condition of the control

circuits (*b* below) and other various operating conditions of the equipment. Secondary signal flow paths, such as indicating and monitoring functions, are also shown.

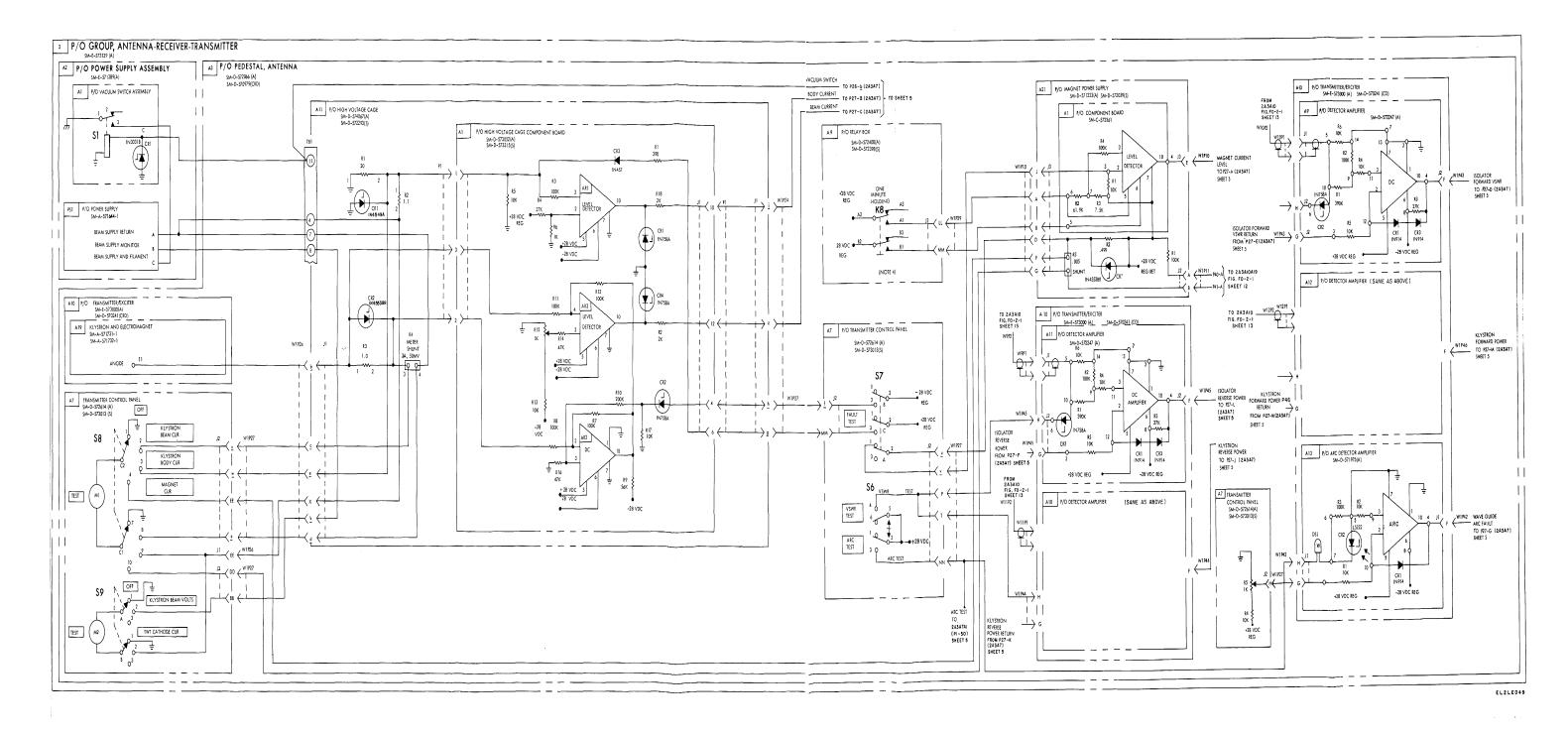

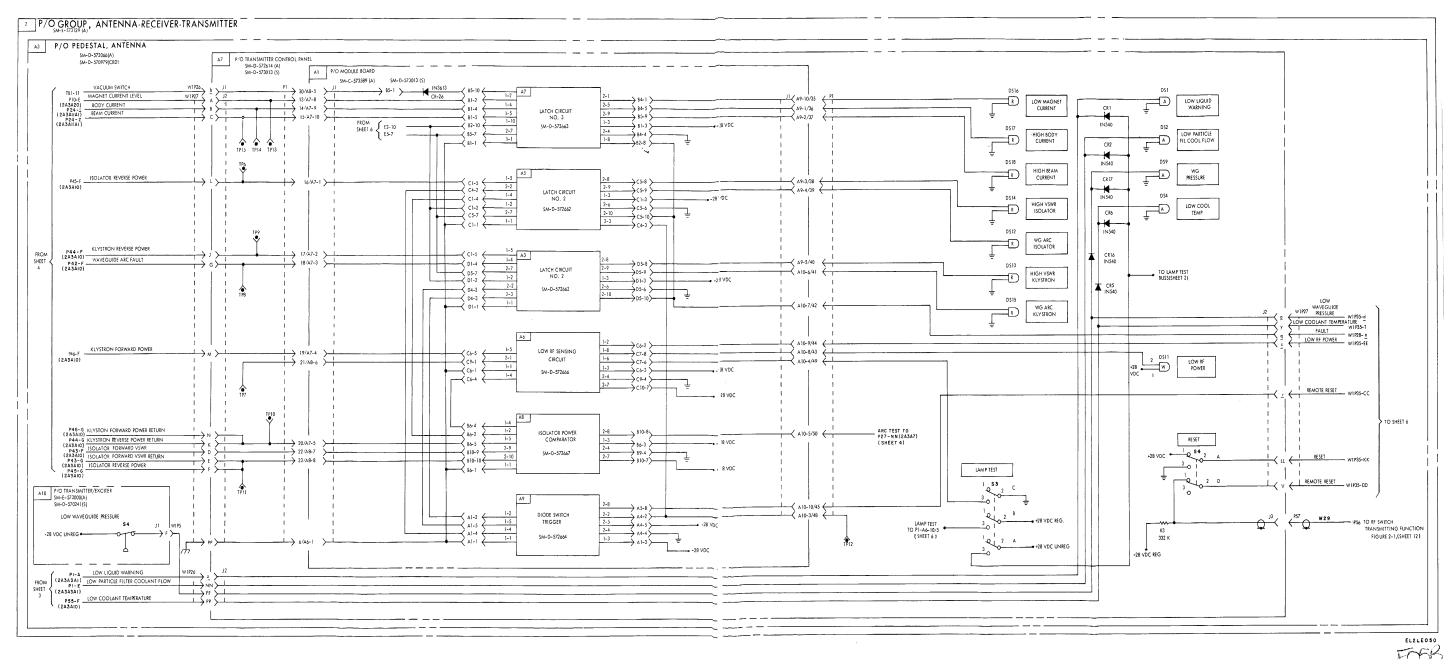

- b. Control Circuit Diagrams. The control circuit diagrams illustrate the application of power to relay solenoids in accordance with specific operating conditions. The relays and associated contacts, in turn, result in an extended sequence of actions to control the circuit path to be taken by a given signal (a above).

- c. Power Distribution Diagrams. The power distribution diagrams illustrate the power input circuits of each component of the AN/TSC-54 and show the complete distribution of alternating current (ac) and direct current (dc) voltages, grounds, and neutrals throughout the equipment, as required by the signal flow (a above) and control (b above) circuits to perform their proper functions.

#### 2-3. Functional Diagram Characteristics

Symbology and other unusual characteristics of functional diagrams are described in a through j below:

- a. Each console or cabinet, modular assembly, subassembly, or unit is identified by an enclosure represented by a dashed line in accordance with the physical breakdown of the equipment. A single dashed line indicates the overall unit or console. Two small dashes in the enclosure indicates the next largest subassembly, etc.

- b. Official nomenclature, assigned names or references designations are used to identify all units, subassemblies, and modular assemblies of the AN/TSC-54 shown on the functional diagrams.

- c. Circuit stages, other than amplifiers (d below), are shown as rectangular blocks.

- d. Amplifier stages are represented by triangular blocks. The point of the triangle indicates the direction of signal flow.

- e. Adjustable and variable components are represented by, their standard symbol and are shown with their assigned reference designation, name, or equipment panel marking. The

method of control (knob or screwdriver) is shown pictorially; screwdriver adjustments are represented by a slotted circle and knob controls are identified by the symbol of a selector knob.

- f. Cross-reference between functions of the equipment and also between the various parts within a particular function are referenced at the outline or periphery of the equipment enclosure.

- g. The functional nomenclature assigned to a circuit, stage, or assembly is descriptive and expressive as possible to establish a clear concept of the item to which it is assigned.

- *h.* Equipment panel markings are capitalized in the text and blocked on the illustrations.

- *i.* Broken lines indicate mechanical connections and solid lines indicate electrical connections.

- *j.* The various abbreviations used for circuit and module identification are as follows:

- (1) Baseband transformer line (BTL).

- Meter compensation network (MCN).

- (3) Equalizing deemphasis network (EDN).

- (4) Twin-tee network (TTN).

- (5) Baseband transformer isolation (BTI).

- (6) Baseband deemphasis network (BDN).

- (7) Baseband preemphasis network (BPN).

- (8) Baseband power amplifier (BPA).

- (9) Baseband operational amplifier (BOA).

- (10) Baseband differential amplifier (BDA).

- (11) Baseband transformer setup (BTS).

- (12) Baseband hybrid transformer (BHT).

#### Section II. TRANSMITTING FUNCTION

#### 2-4. General

- a. This section contains a functional analysis of the transmitting circuits of Satellite Communication Terminal AN/TSC-54. Basically, the terminal is capable of accepting voice, teletypewriter, and wideband multiplexed signals from an external line user, processing these signals and transmitting the signals by way of satellite to a compatible ground terminal.

- Simultaneously, a terminal orderwire, using an operating mode which does not conflict with the user, can transmit on the same radio frequency carrier within the range of 7.to 8.4 GHz.

- b. A functional analysis of the baseband circuits is given in paragraphs 2-5 through 2-10 and paragraphs 2-11 and 2-12 cover the modulator amplifier circuits and operation of Radio Communications Subsystem AN/URC-61. A functional analysis of the rf components of the AN/TSC-54 is covered in paragraphs 2-13 through 2-17; the operation of fault and protective circuits is discussed in paragraphs 2-18 through 2-39.

#### 2-5. Voice Signal Path

(fig. FO 2-1)

The transmitting circuits of the AN/TSC-54 provide one voice channel which can be assigned through landlines to an external user or an orderwire user (terminal user). For purposes of this manual, the user signal path is identified as user voice (a, b, and c below) and the orderwire user signal path is identified as orderwire voice (d through h below).

a. The user voice send signal (sheet 1) is applied to the AN/TSC-54 through USER-1SEND IN terminals EI and E2 and fuses F1 and F2 to filter FL1 of the external signal distribution box 1A10. FL1 offers minimum attenuation to frequencies in the range of 0 to 4 kilohertz (kHz). The output of FL1 is applied through normalized-through USER VOICE NO. 1 EQUIP jacks J33 and J34, USER AMP LINE jacks J9 and J10, and

fuses FI and F2, to the primary winding of baseband line transformer T1. Line isolation is maintained by breakdown diodes CR1 and CR2 which prevent the voltage across the primary winding of T1 from exceeding 7.5 volts. Shunt resistor R35 limits the current flow through the primary winding.

- b. The output from the secondary of T1 is applied as follows:

- (1) Through SEND potentiometer R16B to baseland operational amplifier A17. SEND potentiometer R16B controls the gain of A17.

The output of A17 is applied through baseland operational amplifier A14 and baseland power amplifier A19 to the primary winding of baseland isolation transformer A33. Equalizing deemphasis network All, connected across A14, compensates for any signal envelope distortion.

(2) Through input meter calibrate potentiometer R1 and SEND-RECEIVE switch S1 to baseland operational amplifier A18 and also to meter compensation network A13.

#### **NOTE**

The metering circuits associated with the baseband transmitting function are covered in paragraph 2-9.

c. The nominal O dbm isolated user voice send signal from the secondary of baseband isolation transformer A33 is applied through normalized through USER AMP EQUIP jacks J31 and J32, on patch panel A3 of baseband patch panel 1A3A2, and VOICE SOURCE SEL SWITCH-

USER LINE jacks J7 and J8 to terminals 6 and 8 of VOICE lever switch S1 (sheet 2)

d. For two-wire user application, the hybrid user voice send/receive signal (sheet 1) is applied to the AN/TSC-54 through 2 WIRE-3-SEND/RCV terminals E5 and E6, and fuses F5 and F6 to filter FL3 of the external signal distribution box 1A10. FL3 also offers minimum attenuation to frequencies in the range of 0 to 4 kHz. The output of FL3 is applied through USER VOICE NO. 3 IN/OUT EQUIP jacks J35 and J36, HYBRID COIL 2W OUT/IN LINE jacks J11 and J12, and fuses F1 and F2 to the primary winding of baseband line transformer T1. Breakdown diodes CR1 and CR2 provide line isolation by preventing the voltage across the primary of T1 from exceeding 7.5 volts. The output from the secondary of T1 is applied to baseband hybrid transformer A15 and the outputs of the transformers are applied to HYBRID COIL LINE jacks J23 and J24 and MON jacks J71 and HYBRID COIL LINE jacks J23 and J24 are patched to USER AMP LINE jacks J9 and J10 and the signal path from here on is the same as described in paragraphs a and b above.

#### **NOTE**

For receiving functions, the signal from HYBRID COIL IN EQUIP jacks J47 and J48 is applied in a reverse direction to the external user with the HYBRID COIL IN EQUIP jacks J47 and J48 patched to USER AMP LINE jacks J21 and J22 (FO 2-2, sheet 15).

- e. The orderwire voice signal of the AN/TSC54 originates at handset assembly HS1 (sheet 1). When push-to-talk switch S1 is pressed, a circuit is completed from -28 vdc through resistor R30 to the handset transducer. The output of the transducer is applied across resistor R29 and ORDERWIRE AMPL SEND potentiometer R18B to baseband operational amplifier A52. Potentiometer R18B controls the gain of A52. The output of A52 is amplified by baseband power amplifier A57 and applied to meter calibrate potentiometer R5 and also through normalized-through ORDERWIRE AMP EQUIPMENT jacks J29 and J30 and VOICE SOURCE SEL SWITCH-O/W LINE jacks J5 and J6 to terminals 1 and 3 of VOICE lever switch S1 (sheet 2). The metering circuits used to monitor the orderwire voice signal are discussed in paragraph 2-9.

- f. VOICE lever switch S1 is used to select the user voice signal (d above) or the orderwire voice signal (e above) for application (as the voice send signal) through

normalized-through VOICE SOURCE SEL SW EQUIP jacks J27 and J28 (sheet 3) and ECHO SUPPR TRANSMIT LINE jacks J3 and J4 to echo suppressor transmitter A7. When operating with a two-wire user, the voice send signal is applied through the echo suppressor transmitter A7 to normalled-through ECHO SUPPR TRANSMIT EQUIP jacks J25 and J26 to DERIVATIVE CLIPPER MODE SEL jacks J1 and J2. When operating with a four-wire user, a patch cord is connected between VOICE SOURCE SEL SW EQUIP jacks J27 and J28 and DERIVATIVE CLIPPER MODE SEL LINE jacks J1 and J2 to disconnect the echo suppressor transmitter A7 from the signal path. The voice send signal from DERIVATIVE CLIPPER MODE SEL LINE jacks J1 and J2 is applied to terminals 3 and 6 of CLIPPER lever switch S2 (sheet 4).

- g. When CLIPPER lever switch S2 is set to IN, terminal 6 is grounded and the voice send signal present at terminal 3 is applied to baseband operational amplifier A8. The voice send signal is amplified and clipped by baseband operational amplifiers A8 and A3. During the absence of a voice send signal, baseband operational amplifier A8 receives a 10-kHz squelch signal from a 10-kHz oscillator circuit comprised of baseband operational amplifier A7 and twin-tee network and level control A6. The output of the 10-kHz oscillator circuit is developed across derivative clipper threshold adjust potentiometer R5. Potentiometer R5 is used to adjust the amplitude of the 10-kHz input signal to baseband operational amplifier A8. During the absence of a voice input signal, the 10-kHz squelch signal is amplified and clipped by baseband operational amplifiers A8 and A3 to prevent system noise from being amplified and applied to baseband power amplifier A2. The voice send signal is amplified by baseband power amplifier A2 and is then applied through baseband isolation transformer A1 to terminals 7 and 10 of CLIPPER lever switch S2.

- h. The voice send signal (g above) is applied through closed contacts 7 and 9 and 10 and 12 of CLIPPER lever switch S2 to terminals 4 and 10 of MODE SELECT switch S5A. With CLIPPER lever switch S2 is set to OUT, the voice send signal bypasses the clipper circuits.

- (1) When MODE SELECT switch S5 is set to V1, the voice send signal is applied to VOICE/ TTY FIL TP LINE jacks J1 and J2 on patch panel A2 of baseband patch panel 1A3A2 and through voice/tty filter FL5 to terminals 2 and 8 of switch S5B. VOICE/TTY FIL TP LINE jacks J1 and J2 are used to monitor the voice send signal input to filter FL5 which is a notch type

filter consisting of two sections; a band stop section and a bandpass section. The band stop section passes frequencies in the range of 300 to 1, 180 Hz and 1,370 to 3,500 Hz and offers greater than 60 db rejection to frequencies in the range of 1,180 to 1,370 Hz. The bandpass section passes frequencies in the range from 1.180 Hz to 1.370 Hz and offers greater than 60 db rejection to all other frequencies. This allows the last ditch 1,275 Hz signal to be placed within the voice baseband without interfering with the voice signal. The output of FL5 is applied to terminals 2 and 8 of MODE SELECT switch S5B and to VOICE/TTY FIL LINE EQUIP jacks J25 and J26 and MON jacks J49 and J50 which provide monitoring points for the output of FL5. The signal path from MODE SELECT switch S5 is covered in paragraph 2-7.

- (2) When MODE SELECT switch S5 is set to the V2 position, the voice send signal is applied to terminals 1 and 2 of truncated filter FL3 and to TRUNCATED FIL LINE jacks J3 and J4. TRUNCATED FIL LINE jacks J3 and J4 are used to monitor the voice input signal to FL3 which passes only voice frequencies in the range of 300 to 1,800 Hz. The voice output signal from truncated filter FL3 is applied to contacts 3 and 9 of MODE SELECT switch S5B and to TRUNCATED FIL EQUIP jacks J27 and J28 and MON jacks J51 and J52 which provide the monitoring points for the output of filter FL3.

- (3) When MODE SELECT switch S5 is set to V3, the voice signal is applied to terminals 1 and 2 of normal filter FL1 and to NORMAL FIL LINE jacks J5 and J6. NORMAL FIL LINE jacks J5 and J6 are used to monitor the voice input signal. Filter FL1 passes voice frequencies in the range of 300 to 3,400 Hz and the voice output signal of FL1 is applied to contacts 4 and 10 of switch S5B and to NORMAL FIL EQUIP jacks J29 and J30 and MON jacks J53 and J54 which are used to monitor the output voice signal of filter FL1.

## **2-6.** Teletypewriter Signal Paths (fig. FO 2-1)

The AN/TSC-54 provides one teletypewriter (tty) channel for an external user through landlines and one tty channel for an orderwire user. For purposes of this manual, the external user tty signal is identified as user tty (a and b below) and the orderwire user tty signal is identified as orderwire tty (c and d below). Either the external user or orderwire user may also operate in the last ditch mode (c below).

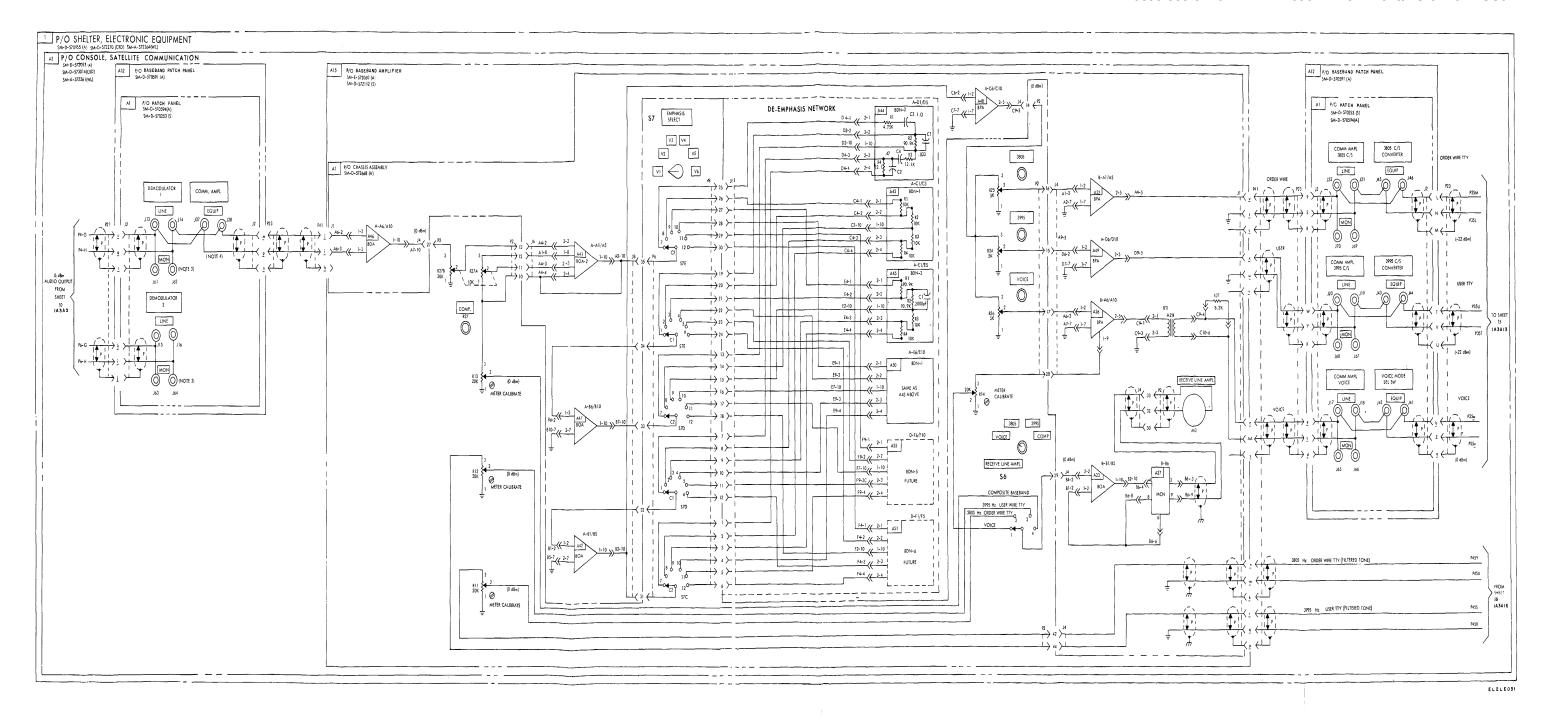

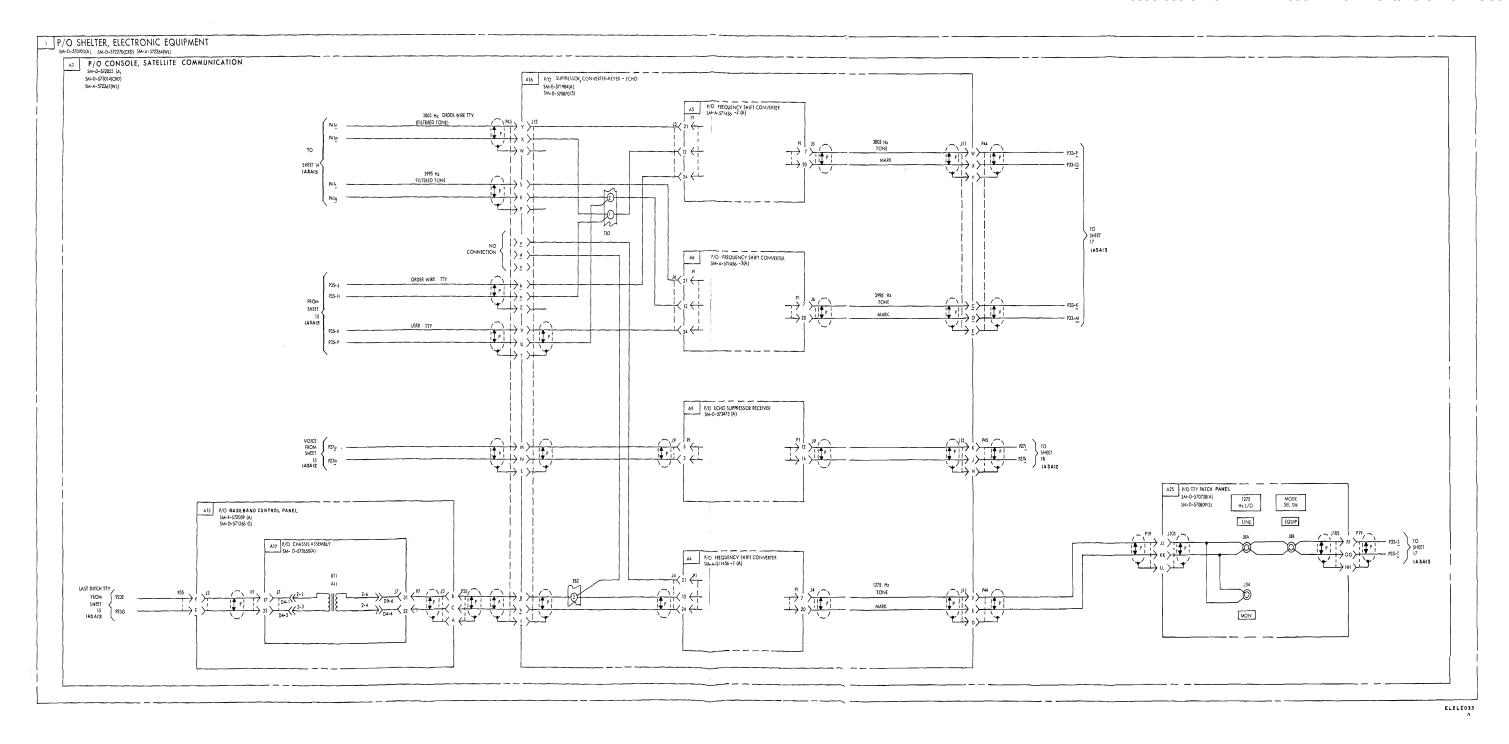

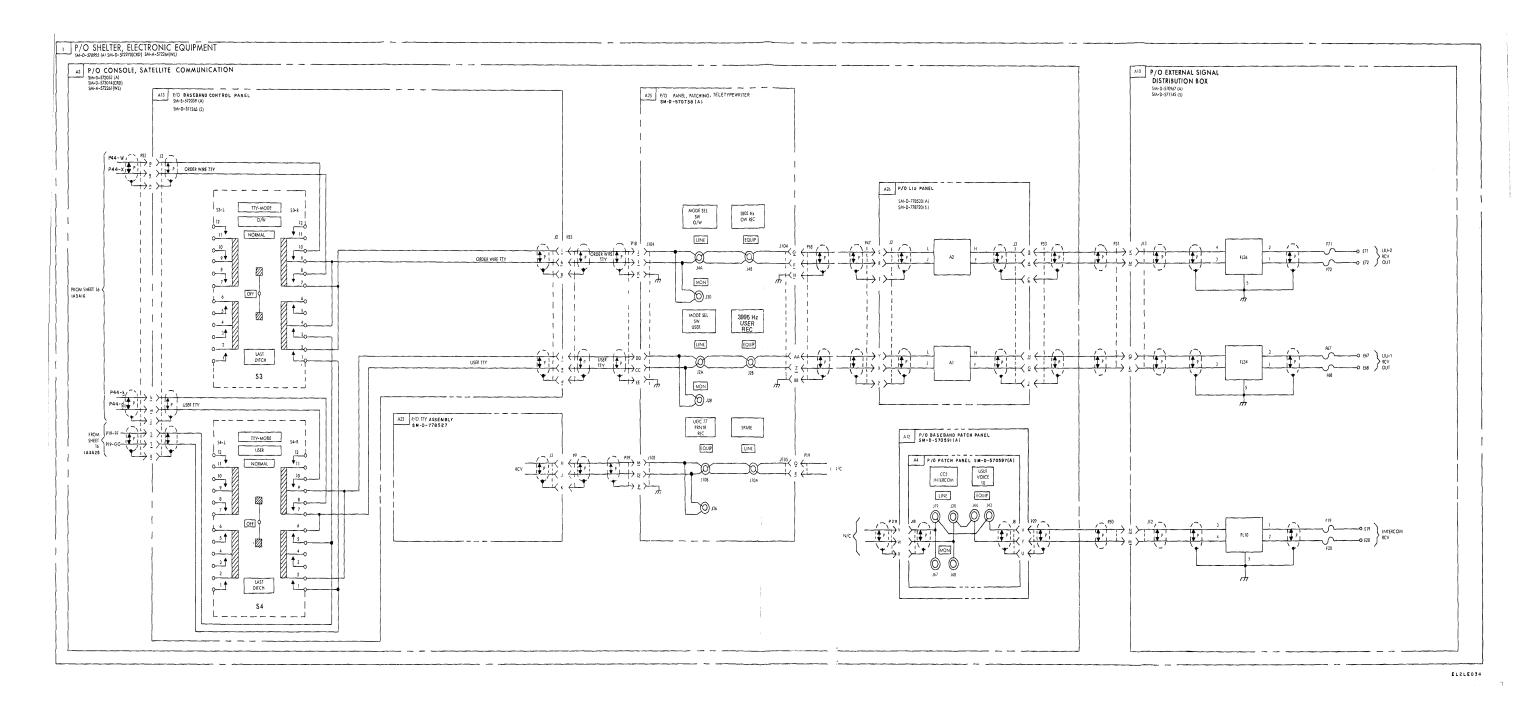

- a. The user tty input signal (sheet 2) is applied to the AN/TSC-54 through LIU-1 SEND IN terminals E65 and E66 and fuses F65 and F66 to filter FL33 of external signal distribution box 1A10. Filter FL33 passes frequencies in the range of 0 to 4 kHz. The output of filter FL33 is applied through J2 pins A and B of the line isolator A1 of line isolation unit 1A3A26, A1 provides isolation between the out-station and in-station signals. A1 also converts the user tty signal to a standard polar +6 volt signal which is applied from J3 pins D and E on the line isolation unit to TX LIU-1 3995 Hz USER EQUIP jack J1B and MON jack J27 on the tty patch panel 1A3A25. EQUIP jack J1B is normalized through to the TTY SEL SW 3995 Hz TX LINE jack J1A. The user tty signal at LINE jack J1A is applied to contacts 7 and 9 of the TTY MODE USER lever switch S4 of baseband control panel 1A3A13. With TTY MODE USER lever switch S4 set to NORMAL, contacts 7 and 8, and 9 and 10 (S4-L) are made and the user tty signal is applied to pins 5, 6, and 16 of the 3995-Hz frequency shift keyer A3 of converter-keyer-echo suppressor 1A3A16 (sheet 3). With the TTY MODE USER lever switch S4 (sheet 2) set to NORMAL, contact 11 and 12 also make and disable the 1275-Hz frequency shift keyer A1 of converter-keyer-echo suppressor 1A3A16 (sheet 3) by completing a ground loop that shorts pins 4 and 14 to inhibit the generation of the 1275-Hz tone. The 3995-Hz frequency shift keyer A3 converts the user dc tty signal to mark and space outputs which are applied from pins 22 and 23 on the frequency shift keyer A3 to the 3995 C/S KEYER EQUIP jacks J31 and J32, and MON jacks J55 and J56 on patch panel A1 of baseband patch panel 1A3A12. The 3995 C/S KEYER EQUIP jacks J31 and J32 are normalized through to COMM AMPL 3995 C/S LINE jacks J7 and J8 to the baseband differential amplifier A5 of baseband amplifier 1A3A15 (sheet 5). The output of differential amplifier A5 is developed across 3995 level adjust potentiometer R22A... The signal at the wiper arm of potentiometer R22A is amplified by baseband operational amplifier A10 and applied as follows:

- (1) Through contact C1 of EMPHASIS SELECT switch S7 to the appropriate preemphasis and deemphasis network.

- (2) Through meter calibrate resistor R7 (sheet 6) to the metering circuits associated with the baseband function.

- b. The orderwire tty signal (sheet 2) is applied to LIU-2-SEND IN terminals E69 and E70, and Fuses F69 and F70 to filter FL35 of external signal distribution box 1A10. Filter FL35 passes frequencies in the range of 0 to 4 kHz. The output of filter FL35 is applied through J2 pins u

and v to line isolator A2 of line isolation unit 1A3A26. A2 functions in a manner identical to A1 described in a above. The output of A2 is applied from J3 pins X and Y on the line isolation unit to TX LIU-2 3805 Hz OW EQUIP jack J3B and MON jack J29 on the tty patch panel 1A3A25. EQUIP jack J3B which is normalized through to the TTY SEL SW 3805 Hz TX LINE jack J3A applies the signal to contacts 7 and 9 of TTY MODE ORDERWIRE lever switch S3 of baseband control panel 1A3A13. With TTY MODE ORDERWIRE lever switch S3 set to NORMAL, contact 7 and 8, and 9 and 10 (S3-L) are made, and the orderwire tty signal is applied to pins 5, 6, and 16 of the 3805-Hz frequency shift keyer A2 of converter-keyer-echo suppressor 1A3A16. With TTY MODE ORDERWIRE lever switch S3 (sheet 2) set to NORMAL, contacts 11 and 12 (S3-L) also make and disable the 1275-Hz frequency shift keyer A1 of converter-keyer-echo suppressor 1A3A16 (sheet 3) to inhibit the generation of the 1275-Hz tone. The 3805-Hz frequency shift keyer A2 converts the dc orderwire tty signal to mark and space frequency outputs which are applied to the 3805 C/S keyer EQUIP jacks J33 and J34 and MON jacks J57 and J58 on patch panel A1 of baseband patch panel 1A3A12. EQUIP jacks J33 and J34 are normalized-through to COMM AMPL 3805 C/S LINE jacks J9 and J10 to baseband differential amplifier A3 of baseband amplifier 1A3A15 (sheet 5). The output of baseband differential amplifier A3 is developed across 3805 level adjust potentiometer R21A and is amplified by baseband operational amplifier A4 and applied as follows:

- (1) Through contact C1 of EMPHASIS SELECT switch S7 to the appropriate preemphasis and deemphasis network.

- (2) Through meter calibrate resistor R8 (sheet6) to the metering circuits associated with the orderwire tty signal.

### NOTE

The send signal from connector J2 pins A and B on the UGC-77 teletypewriter assembly 1A3A23 (sheet 2), is applied to TX UGC-77 KEYER PTR EQUIP jack J9B and MON jack J35 on the tty patch panel 1A3A25. In the event the UGC-77 is to be used as the orderwire user, EQUIP jack J9B must be patched to TTY SEL SW 3805 TX LINE jack J3A.

- c. The last ditch tty send mode may be used for a user tty input (a above) or the orderwire tty input (b above). When either a user tty input or the orderwire input is selected for last ditch operation, the associated frequency shift keyer is disabled and the 1275-Hz frequency shift keyer is enabled.

- (1) When TTY MODE USER lever switch S4 of baseband control panel 1A3A13 (sheet 2) is set to LAST DITCH, a ground loop is completed through contacts 3 and 4 of switch S4 (S4-R) disabling the 3995-Hz frequency shift keyer A3 of converter-keyer-echo suppressor 1A3A16 (sheet 3). The 1275-Hz frequency shift keyer, of 1A3A16, is enabled by open contacts 11 and 12 of switch S4 (S4-L) and the dc input to the 3995-Hz frequency shift keyer A3 is opened by contacts 7 and 8. With TTY MODE USER switch S4 (sheet 2) set to LAST DITCH, contacts 1 and 2, and 5 and 6 are also made, which applied the user tty signal to TX TTY SEL SW 1275 Hz L/D EQUIP jack J7B and MON jack J33 on the tty patch panel 1A3A25 (sheet 3). EQUIP jack J7B is normalized-through to KEYER CONV 1275 Hz TX LINE jack J7A. The user tty signal at J7A is applied to pins 5, 6, and 16 of the 1275-Hz frequency shift keyer A1 of converter-keyer-echo suppressor 1A3A16. The output signal at pins 22 and 23 of the 1275-Hz frequency shift keyer A1 is applied to the 1275 C/S KEYER EQUIP jacks J35 and J36, and MON jacks J59 and J60 on patch panel A1 of baseband patch panel 1A3A12.

EQUIP jacks J35 and J36 are normalized through to VOICE/TTY TG LINE jacks J11 and J12. The signal at LINE jacks J11 and J12 is applied through pins f and g of connector P32, to pins 3 and 4 of voice/tty filter A17FL5 of baseband control panel 1A3A13 (sheet 4). The output of A17FL5 is identical to that discussed in paragraph 2-5h(1).

(2) When TTY MODE ORDERWIRE switch S3 of baseband control panel 1A3A13 (sheet 2) is set to LAST DITCH, a ground loop is completed through contacts 5 and 6 of switch S3 (S3-R) to disable the 3805-Hz frequency shift keyer A2 of converter-keyer-echo suppressor 1A3A16 (sheet 3). The 1275-Hz frequency shift keyer 1A, of 1A3A16, is enabled by opening contacts 11 and 12 of switch S3 (S3-L) and the dc input path of the 3805-Hz frequency shift keyer A2 is opened by contacts 9 and 10. With TTY MODE ORDERWIRE switch S3 (sheet 2) set to LAST DITCH, contacts 9 and 10. With TTY MODE ORDERWIRE switch S3 (sheet 2) set to LAST DITCH, contacts 1, 2, 3, and 4 (S3-L) are made and apply the orderwire tty signal to TX TTY SEL SW 1275 Hz L/D EQUIP jack J7B and MON jack J33 on the tty patch panel 1A3A25 (sheet 3).

The signal path from EQUIP jack J7B is identical to the user tty signal path discussed in (1) above.

### 2-7. Wideband Multiplex Signal (Transmit

(fig. FO 2-1, sheet 4)

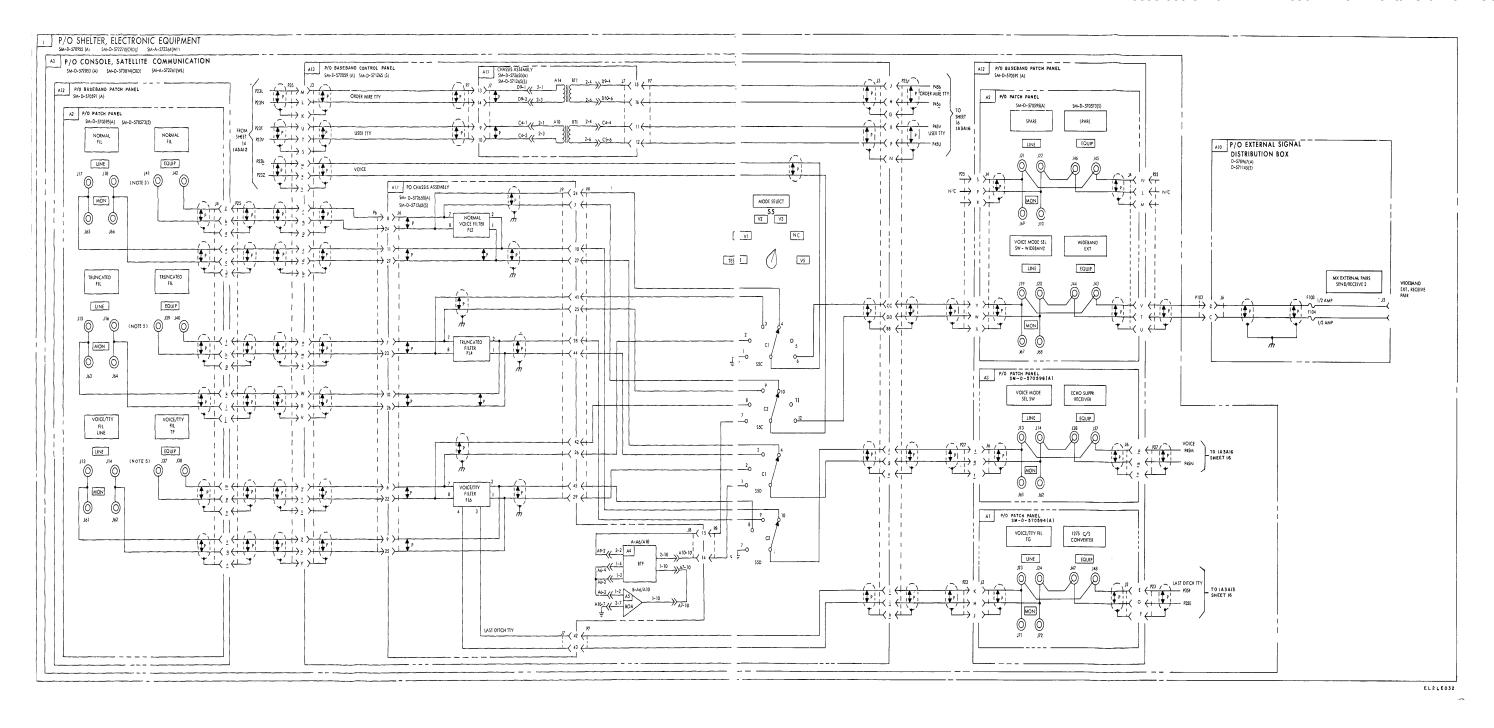

The wideband multiplex send signal is applied the AN/TSC-54 through wideband external input jack J4 and fuses F101 and F102, of t external signal distribution box 1A10, normalized-through WIDEBAND EXT EQU jacks J31 and J32, MON jacks J55 and J56, a VOICE MODE SEL SW WIDEBAND LIE jacks J7 and J8 on patch panel A2 of baseband patch panel 1A3A12, and then through baseband isolation transformer A17A9 to contacts 6 and 12 of MODE SELECT switch S5B baseband control panel 1A3A13. When t MODE SELECT switch is set to V5, the wideband multiplex signal is selected as discussed paragraph 2-8.

### 2-8. Composite Voice and Teletypewriter Signal

(fig. FO 2-1)

- a. The following modes of operation can selected with MODE SELECT switch S5 baseband control panel 1A3A13 (sheet 4):

- (1) Position V1 selects the output of vc tty filter A17A5 which consists of voice frequencies in the range of 300 to 1,180 Hz, 1,370 to 3,1 Hz, and the last ditch tty frequency of 1,275 I

- (2) Position V2 selects the output of truncated filter A17FL3 which consists of voice frequencies in the range of 300 to 1,800 Hz.

- (3) Position V3 selects the 300 to 3,400 voice frequency output of normal filter A17F

- (4) Position V4 is not connected.

- (5) Position V5 selects the 0 to 23 kHz multiplex wideband signal.

- b. The composite voice/tty signal (0 dbm level is applied from contacts C1 and C2 of MO] SELECT switch S5B, normalized-through VOICE MODE SEL SW EQUIP jacks S29 a J30, MON jacks J53 and J54, and COMM AM VOICE LINE jacks J5 and J6 to baseband differential amplifier A1 (sheet 5). The amplified o put of baseband differential amplifier A1 is developed across VOICE potentiometer R20A. signal at the wiper arm of potentiometer R2 is amplified by baseband operational amplifierA6 and applied as follows:

- (1) Through contact C1 of EMPHASIS SELECT switch S7 to the appropriate preemphasis and deemphasis network.

- (2) Through meter calibrate potentiometer 1A3A15R9 (sheet 6) to the associated meter circuits.

- c. The user tty 3995-Hz fsk signal, the orderwire tty 3805-Hz fsk signal, and the composite, voice/tty signals are combined at EMPHASIS SELECT control switch 1A3A15S7 (sheet 5) to complete the baseband frequency composition. The selected preemphasis network accentuates the higher baseband frequencies to improve the signal-to-noise ratio when the signal is used to modulate the carrier frequency. The output of he selected preemphasis network is applied to COMP potentiometer R23 which is used to adjust the amplitude of the input signal applied to baseband power amplifier 1A3A15A1A8 (sheet 6). The amplified output of baseband power n amplifier A8 is applied through contacts 1 and 3 of armature relay A12 to meter calibrate potentiometer R10 and through pin J of connector J1 n to normalized-through COMM AMPL EQUIP jacks J25 and J26, MON jacks J49 and J50, and MODULATOR LINE jacks J1 and J2. The baseband signal from LINE jacks J1 and J2 is 9' applied to modulation amplifier A1 in modulator 1A3A14 (sheet 7) (para 2-11).

#### 2-9. Baseband Metering Circuit

(fig. FO 2-1)

The metering circuits associated with the baseband send function are discussed in a through d below:

- USER LINE AMPL LEVEL meter 1A3A15M1 (LEVEL-meter M1) (sheet 1) and its associated circuit .components are used to monitor the user voice input and user voice output signals of baseband amplifier A15. When USER LINE AMPL SEND-RECEIVE control switch S1 (SEND-RECEIVE control switch S1) is set to SEND IN, the developed across input signal, meter calibrate potentiometer R1, is applied through baseband operational amplifier A18 and meter compensation network A13 to LEVEL meter M1. With SEND-RECEIVE control switch S1 set to SEND OUT, the output signal developed across meter calibrate potentiometer R2 is applied to LEVEL meter M1. Meter compensation network A13 provides protection for the meter by ensuring that the output signal applied does not exceed a safe level; it also provides a small deflection voltage to deflect the pointer to the first meter division on the scale, thus ensuring that the meter pointer is not resting against a stop when the input signal is received. Meter calibrate potentiometers R1 and R2 are adjusted for a zero meter, indication with a 0-dbm input signal to baseband amplifier A15.

- b. Vu LEVEL meter M2 and its associated circuit components are used to monitor the orderwire voice input to baseband amplifier A15. With SEND-RECEIVE switch S2 set to SEND,

the orderwire voice signal, developed across meter calibrate resistor R5 is applied to baseband operational amplifier A53. The amplified output signal is applied through meter compensation network A58 to LEVEL meter M2. The compensation network is provided so that identical meters can be used in various circuits and can be calibrated to indicate 0 vu over a wide range of input signal levels. The meter compensation network also insures that the output to the meter does not exceed a safe level Meter calibrate potentiometer R5 is adjusted for a zero meter indication when the input signal level is known to be correct. c. Vu SEND LINE AMPL meter M4 (sheet 6: and its associated circuit components are used to monitor the baseband voice, 3805 teletypewriter, 3995 teletypewriter, and the composite baseband signals. SEND LINE AMPL selector switch S4 receives all the signals to be monitored from the wiper arms of meter calibrate potentiometers R7 through R10 and applies the selected signal to baseband operational amplifier A24. signal is amplified by baseband operational amplifiers A24 and A30 and applied through meter compensation network A28 to Vu SEND LINE AMPL meter M4. The compensation network provides compensation so that identical meters can be used in various circuits and can be calibrated to indicate 0 vu over a wide range of input signals levels; it also provides protection by ensuring that the output signal to the meter does not exceed a safe level.

- d. VOLTMETER M2 (sheet 3) on the baseband control panel is used to monitor dc tty signal voltages. In order to monitor these voltages, a patch must be made on the tty patch panel 1A3A25 between +6V METER jack (J76) and the monitor jack corresponding to the tty channel of interest.